目 录

前 言

1 工程编译、程序加载方法

1.1 工程编译

1.2 程序加载

2 led-flash

2.1 案例说明

2.2 操作说明

2.3 关键代码

更多帮助

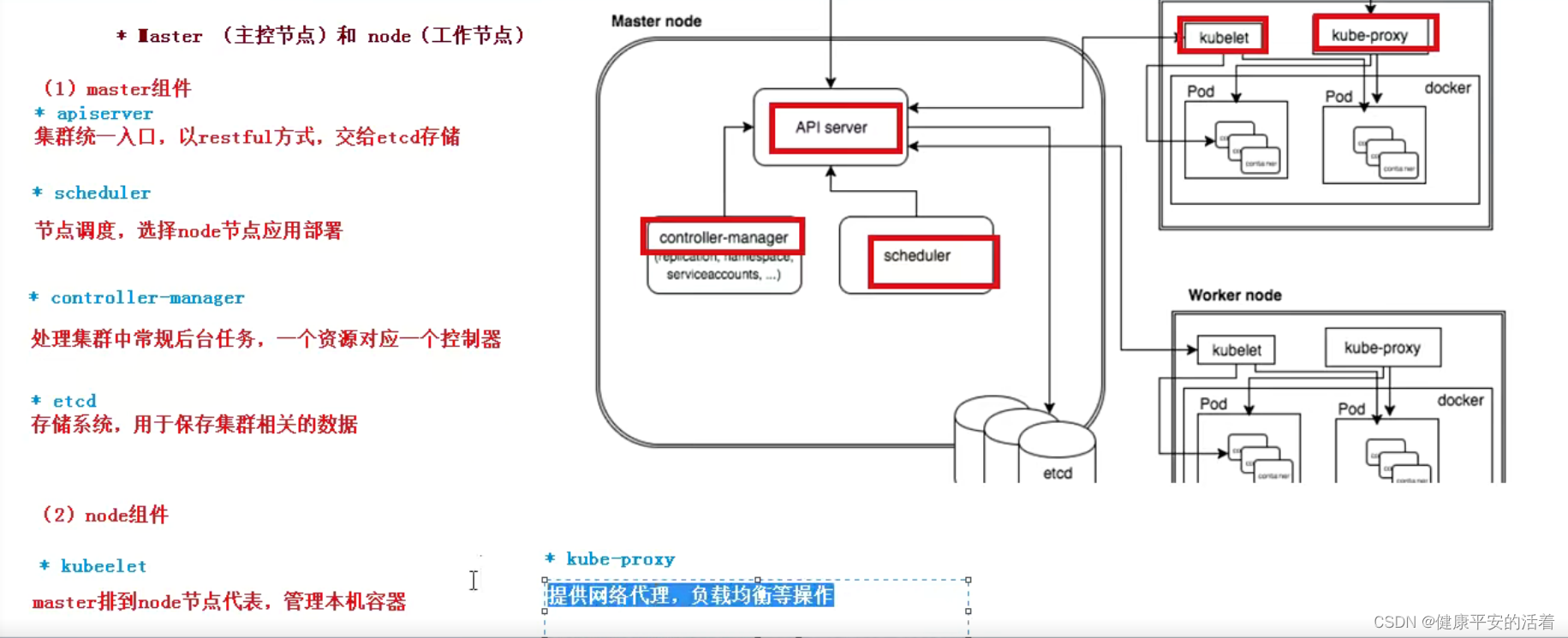

前 言

本文主要介绍PL端案例的使用说明,适用开发环境:Windows 7/10 64bit、Xilinx Unified 2022.2。在进行本文如下操作前,请先按照调试工具安装文档安装Xilinx Unified 2022.2开发工具包。本文默认使用创龙科技的TL-DLC10下载器进行操作演示,请使用下载器连接评估板JTAG接口至PC端USB接口。

注:本案例基于创龙科技Xilinx UltraScale+ MPSoC系列XCZU7EV高性能处理器设计的高端异构多核SoC工业核心板

PL端案例位于产品资料“4-软件资料\Demo\FPGA-HDL-demos\”目录下,案例使用Verilog语言进行开发。案例包含project和bin两个目录,其中project目录下包含案例工程文件,bin目录下含有案例可执行文件。案例目录详细说明见下表:

表 1

| 目录 | 文件/目录 | 说明 |

| bin | xxx_xczu7ev.bin/xxx_xczu7ev.bit | PL端可执行文件 |

| project | PL端Vivado工程 | |

处理器硬件资源详细开发说明可查阅产品资料“6-开发参考资料\数据手册\核心板元器件\ZYNQ\”目录下的文档。

本章节以产品资料“4-软件资料\Demo\FPGA-HDL-demos\”目录下的led_flash案例为例,演示工程编译、程序加载等相关操作方法。此案例的功能是PL端控制评估底板的LED2进行闪烁。

请将对应案例目录拷贝至Windows非中文路径下。

备注:Windows路径有长度限制,路径太长将会导致工程打开出错。

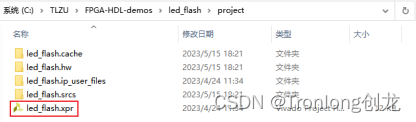

进入案例工程对应平台目录,双击.xpr文件打开Vivado工程。

图 1

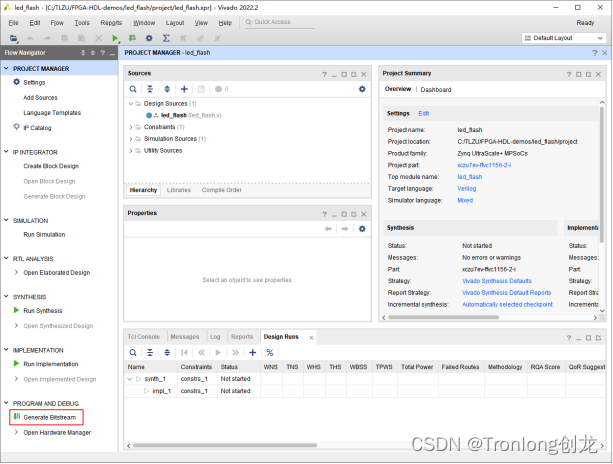

在弹出的界面中,点击左边"PROGRAM AND DEBUG"栏目下的"Generate Bitstream"选项。

图 2

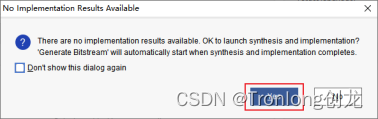

如弹出如下对话框,请点击Yes。

图 3

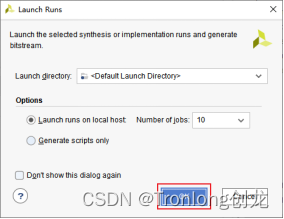

弹出如下界面,请点击OK。

图 4

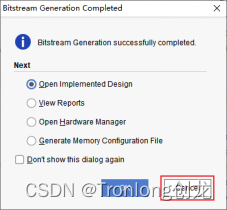

耗时约3~6min后,工程编译完成,编译时间与PL端工程大小、PC机性能相关。编译完成后,将弹出如下界面,请点击Cancel即可。

图 5

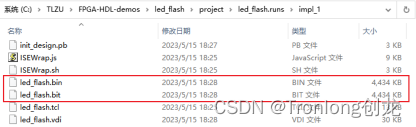

此时将在案例工程目录的"xxx.runs\impl_1\"路径下生成PL端.bit与.bin格式可执行文件。其中.bit文件一般通过下载器进行加载运行,.bin文件可基于PS端加载运行。

图 6

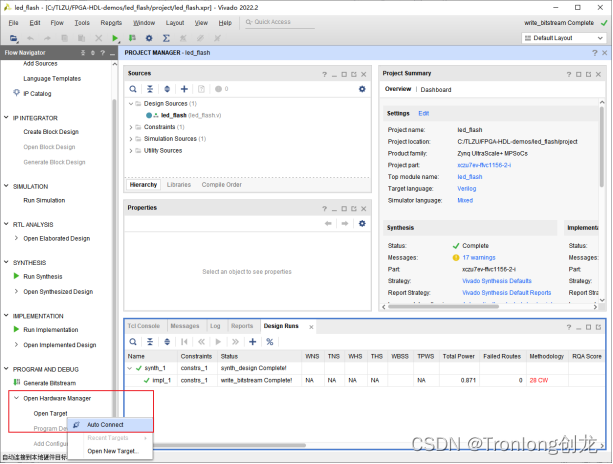

请将评估板启动方式选择拨码开关设置为0000(1~4),此档位为JTAG模式,再将评估板上电。将Vivado界面左下角的"Open Hardware Manager"栏目展开,点击"Open Target"后点击"Auto Connect"选项。

图 7

等待Vivado识别评估板,识别成功后如下图所示。

图 8

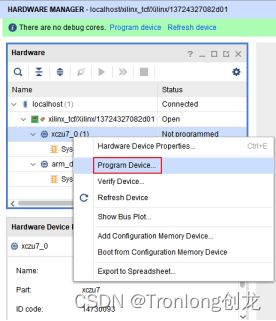

右击xczu7_0后点击"Program Device…"选项。

图 9

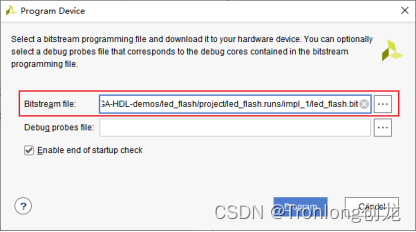

在弹出界面的"Bitstream file"栏,选择待加载的PL端.bit格式可执行文件,已编译的工程将会自动选择,再点击Program进行加载。

图 10

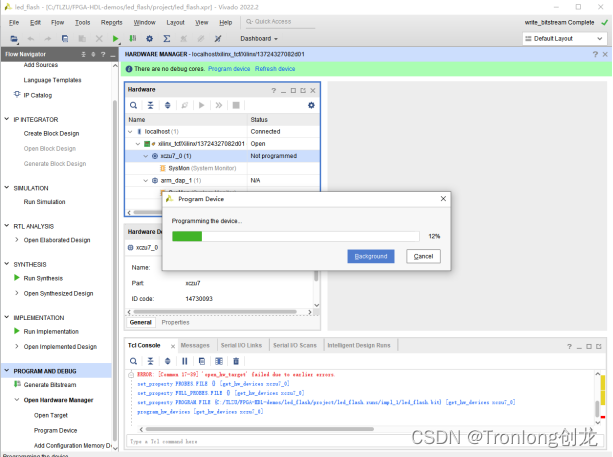

图 11

加载完成后,即可看到评估底板的LED2进行闪烁,说明程序基于下载器加载并运行成功。

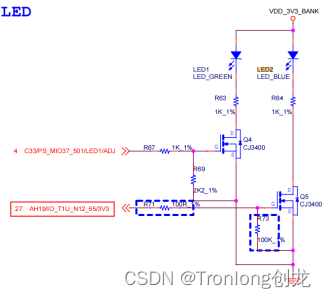

案例功能:控制评估底板LED2每隔0.5s将状态翻转一次。

管脚约束请查看案例工程"xxx.srcs\constrs_1\imports\constraints\"目录下的.xdc文件。

图 12

程序运行后,即可看到评估底板的LED2进行闪烁,

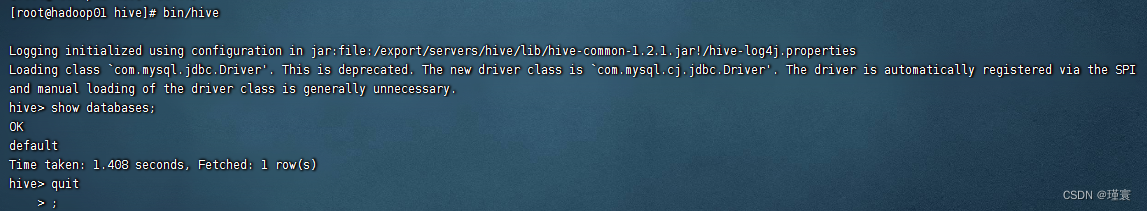

顶层文件为"led_flash\project\led_flash.srcs\sources_1\imports\hdl\led_flash.v",关键代码说明如下。

- 根据50MHz时钟定义0.5s延时计数值。

![]()

图 13

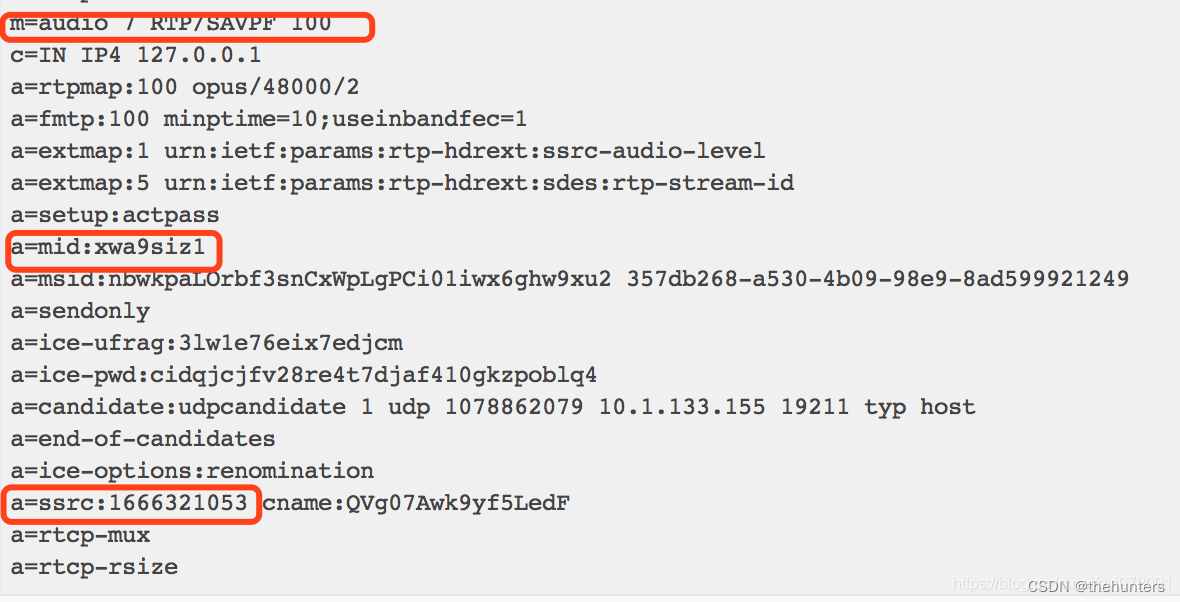

- 使用STARTUPE3原语提供LED时钟及复位。

![]()

图 14

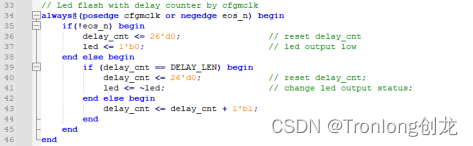

- 使用eos_n信号对LED延时进行复位;延时计数值累计次数达到设定的延时值,则翻转LED输出状态。

图 15

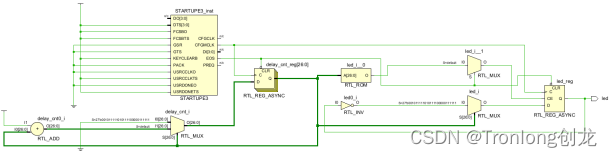

RTL原理图如下所示:

图 16