参考《 Cortex-A7 Technical ReferenceManua.pdf 》和《 ARM Cortex-A(armV7) 编程手

册 V4.0.pdf 》

【 正点原子】I.MX6U嵌入式Linux驱动开发指南V1.6学习

1.Cortex-A7 MPCore 简介

I.MX6UL 使用的是 Cortex-A7 架构,Cortex-A7 MPcore 处理器支持 1~4 核,官方描述:

“在 28nm 工艺下, Cortex-A7 可以运行在 1.2~1.6GHz ,并且单核面积不大于 0.45mm 2 ( 含

有浮点单元、 NEON 和 32KB 的 L1 缓存 ) ,在典型场景下功耗小于 100mW , 这使得它非常适

合对功耗要求严格的移动设备,这意味着 Cortex-A7 在获得与 Cortex-A9 相似性能的情况下,

其功耗更低”

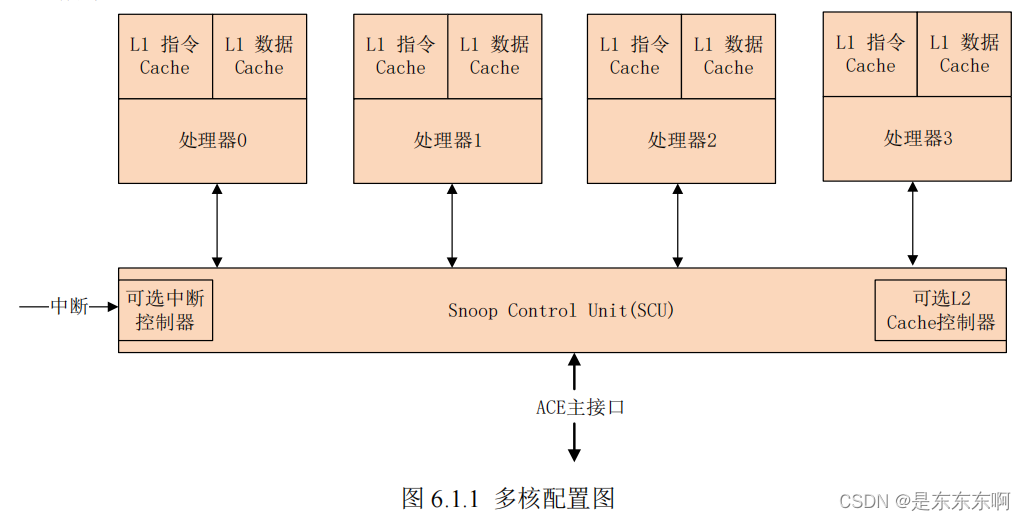

Cortex-A7 MPCore 支持在一个处理器上选配 1~4 个内核, Cortex-A7 MPCore 多核配置如图:

Cortex-A7 MPCore 的 L1 可选择 8KB 、 16KB 、 32KB 、 64KB , L2 Cache 可以不配,也可以

选择 128KB 、 256KB 、 512KB 、 1024KB 。 I.MX6UL 配置了 32KB 的 L1 指令 Cache 和 32KB 的

L1 数据 Cache ,以及 128KB 的 L2 Cache 。 Cortex-A7MPCore 使用 ARMv7-A 架构,主要特性如下:

①、SIMDv2 扩展整形和浮点向量操作。

②、提供了与 ARM VFPv4 体系结构兼容的高性能的单双精度浮点指令,支持全功能的

IEEE754。

③、支持大物理扩展(LPAE) ,最高可以访问 40 位存储地址,也就是最高可以支持 1TB 的

内存。

④、支持硬件虚拟化。

⑥、支持 Generic Interrupt Controller(GIC)V2.0 。

⑦、支持 NEON ,可以加速多媒体和信号处理算法。

补充:

(1) 高速缓存

CPU和主存之间也存在多级高速缓存,一般分为3级,分别是L1, L2和L3。另外,我们的代码

都是由2部分组成: 指令和数据。L1 Cache比较特殊,每个CPU会有2个L1 Cache。分别为指令高

速缓存(Instruction Cache,简称iCache)和数据高速缓存(Data Cache,简称dCache)。L2和L3

一般不区分指令和数据,可以同时缓存指令和数据。

iCache的作用是缓存指令,dCache是缓存数据。 为什么我们需要区分数据和指令呢?原因之

一是出于性能的考量。CPU在执行程序时,可以同时获取指令和数据,做到硬件上的并行,提升性

能。

(2) 什么是流水线技术?

流水线(Pipeline)技术是指程序在执行时候 多条指令重叠进行操作的一种 准并行处理实现技术。

在流水线中一条指令的生命周期分为: 取指、译指、执行、访存、写回。

2.Cortex-A 处理器运行模型

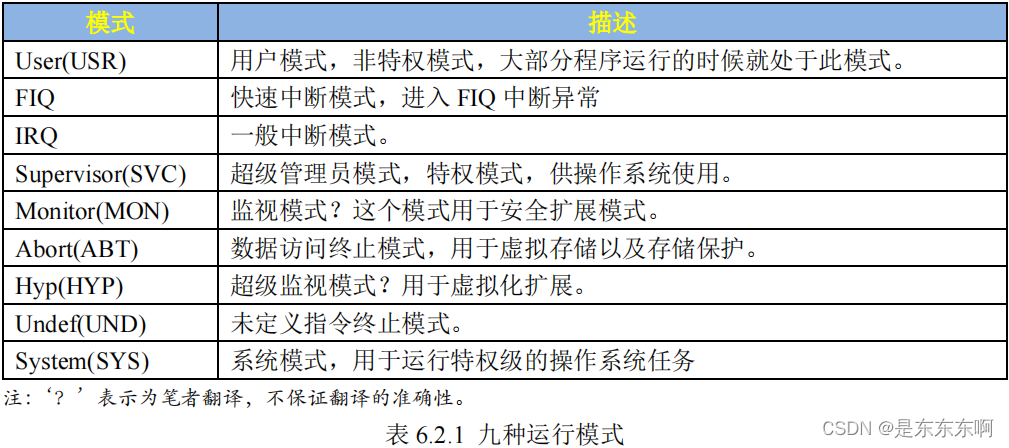

Cortex-A7 处理器有 9 种处理模式:

除了 User(USR) 用户模式以外,其它 8 种运行模式都是特权模式,除了 用户模式和SVC模

式,其它7种都异常模式,大多数的程序都运行在用户模式,用户模式下是不能访问系统所有资源

的,有些资源是受限的,要想访问这些受限的资源就必须进行模式切换,但是用户模式是不能直接

进行切换的, 用户模式下需要借助异常来完成模式切换,当要切换模式的时候,应用程序可以产生

异常,在异常的处理过程中完成处理器模式切换。

当中断或者异常发生以后,处理器就会进入到相应的异常模式中,每一种模式都有一组寄

存器供异常处理程序使用,这样的目的是为了保证在进入异常模式以后,用户模式下的寄存器

不会被破坏。

而相比于我们经常使用的 STM32只有特权模式和非特权模式。

3.Cortex-A 寄存器组

3.1 总体介绍

参考 《ARM Cortex-A(armV7) 编程手册 V4.0.pdf 》的“第 3 章 ARM Processor ModesAnd Registers” 。

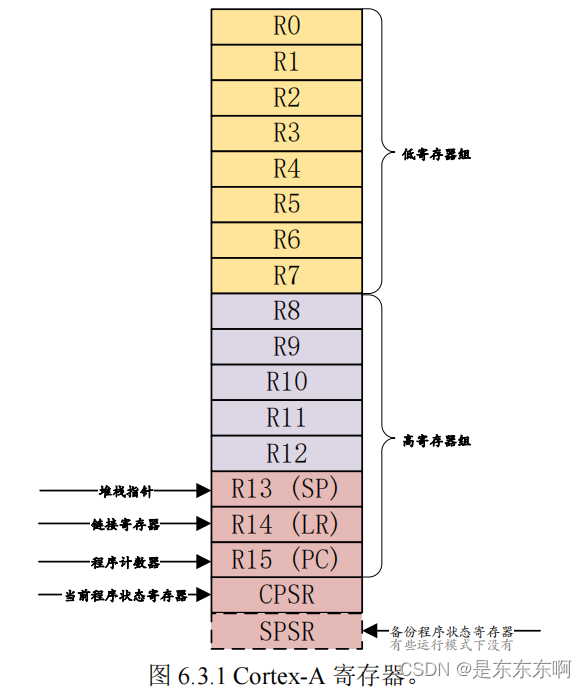

Cortex-A 的内核寄存器组,注意不是芯片的外设寄存器。

ARM 架构提供了 16 个 32 位的通用寄存器 (R0~R15) 供软件使用,前 15 个 (R0~R14) 可以用

作通用的数据存储,R15 是程序计数器 PC,用来保存将要执行的指令。ARM还提供了一个当前程

序状态寄存器CPSR和它的备份寄存器SPSR。

注意几个特殊寄存器: 堆栈指针R13、链接R14、程序计数器(PC)R15

Cortex-A7 有 9 种运行模式,每一种运行模式都有一组与之对应的寄存 器组。每一种模式可见

的寄存器包括 15 个通用寄存器 (R0~R14) 、一两个程序状态寄存器和一个 程序计数器 PC。在这些

寄存器中,有些是所有模式所共用的同一个物理寄存器,有一些是各模 式自己所独立拥有的。在

所有的模式中,低寄存器组 (R0~R7)是共享同一组物理寄存器的, 一些高寄存器组在不同的模式有

自己独有的寄存器。

总结一下,Cortex-A 内核寄存器组成如下:

①、34 个通用寄存器,包括 R15 程序计数器 (PC) ,这些寄存器都是 32 位的。

②、8 个状态寄存器,包括 CPSR 和 SPSR 。

③、Hyp 模式下独有一个 ELR_Hyp 寄存器。

3.2通用寄存器分类

R0~R15 就是通用寄存器,通用寄存器可以分为以下三类:

①、未备份寄存器,即 R0~R7 。

②、备份寄存器,即 R8~R14 。

③、程序计数器 PC ,即 R15 。

分别来看一下这三类寄存器:

1、未备份寄存器

未备份寄存器指的是 R0~R7 这 8 个寄存器,因为在所有的处理器模式下这 8 个寄存器都是

同一个物理寄存器,在不同的模式下,这 8 个寄存器中的数据就会被破坏。所以这 8 个寄存器并

没有被用作特殊用途。

2、备份寄存器

备份寄存器中的 R8~R12 这 5 个寄存器有两种物理寄存器,在快速中断模式下 (FIQ) 它们对

应着 Rx_irq(x=8~12) 物理寄存器,其他模式下对应着 Rx(8~12) 物理寄存器。

FIQ 是快速中断模式,FIQ 模式下中断处理程序可以使用 R8~R12寄存器,因为 FIQ 模式下

的 R8~R12 是独立的,因此中断处理程序可以不用执行保存和恢复中断现场的指令,从而加速中

断的执行过程。

备份寄存器 R13 一共有 8 个物理寄存器,其中一个是用户模式 (User) 和系统模式 (Sys) 共用

的,剩下的 7 个分别对应 7 种不同的模式。 R13 也叫做 SP ,用来做为栈指针。基本上每种模式

都有一个自己的 R13 物理寄存器,应用程序会初始化 R13 ,使其指向该模式专用的栈地址,这

就是常说的初始化 SP 指针。

备份寄存器 R14 一共有 7 个物理寄存器,其中一个是用户模式 (User) 、系统模式 (Sys) 和超

级监视模式 (Hyp) 所共有的,剩下的 6 个分别对应 6 种不同的模式。R14 也称为链接寄存器 (LR) ,

LR 寄存器在 ARM 中主要用作如下两种用途:

①、每种处理器模式使用 R14(LR) 来存放当前子程序的返回地址,如果使用 BL 或者 BLX 来调用

子函数的话,R14(LR) 被设置成该子函数的返回地址,在子函数中,将 R14(LR) 中的值赋给

R15(PC) 即可完成子函数返回。相当于将执行流程跳转回子函数的下一条指令,从而实现函数的

返回。例如:

SubFunction:

...

MOV R0, #42 ; 子函数中的一些操作

...

MOV PC, LR ; 将 R14(LR)的值赋给 R15(PC),完成函数返回

②、当异常发生以后,该异常模式对应的 R14 寄存器被设置成该异常模式将要返回的地址, R14

也可以当作普通寄存器使用。

3、程序计数器 R15

程序计数器 R15 也叫做 PC ,R15 保存着当前执行的指令地址值加 8 个字节,这是因为 ARM

的流水线机制导致的。

ARM 处理器 3 级流水线: 取指->译码->执行,这三级流水线循环执行,比如当前正在执行第

一条指令的同时也对第二条指令进行译码, 第三条指令也同时被取出存放在 R15(PC)中。我们喜

欢以当前正在执行的指令作为参考点,也就是 以第一条指令为参考点,那么 R15(PC)中存放的就

是第三条指令,换句话说就是 R15(PC)总是指向当前正在执行的指令地址再加上 2 条指令的地

址。对于 32 位的 ARM 处理器,每条指令是 4 个字节,所以:

R15 (PC) 值 = 当前执行的程序位置 (取值) + 8 个字节。

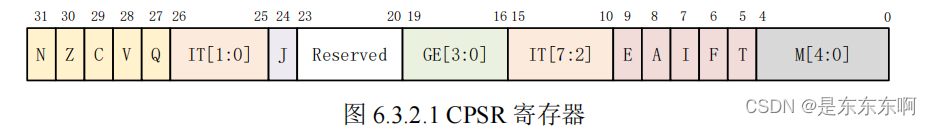

3.3 程序状态寄存器

所有的处理器模式都共用一个 CPSR 物理寄存器,因此 CPSR 可以在任何模式下被访问。

CPSR 是当前程序状态寄存器,该寄存器包含了条件标志位、中断禁止位、当前处理器模式标志

等一些状态位以及一些控制位。所有的处理器模式都共用一个 CPSR 必然会导致冲突,为此,

除了 User 和 Sys 这两个模式以外,其他 7 个模式每个都配备了一个专用的物理状态寄存器,叫

做 SPSR( 备份程序状态寄存器 ) ,当特定的异常中断发生时, SPSR 寄存器用来保存当前程序状

态寄存器 (CPSR) 的值,当异常退出以后可以用 SPSR 中保存的值来恢复 CPSR 。

因为 User 和 Sys 这两个模式不是异常模式,所以并没有配备 SPSR ,因此不能在 User 和

Sys 模式下访问 SPSR ,会导致不可预知的结果。由于 SPSR 是 CPSR 的备份,因此 SPSR 和

CPSR 的寄存器结构相同。

总结:所有的处理器模式共用一个CPSR,CPSR可以在任何模式下被访问,SPSR只能在异常模

式被访问,SPSR作用就是在保存异常前正常的CPSR值。

可以通过M[4:0]位来设置处理器的工作模式。