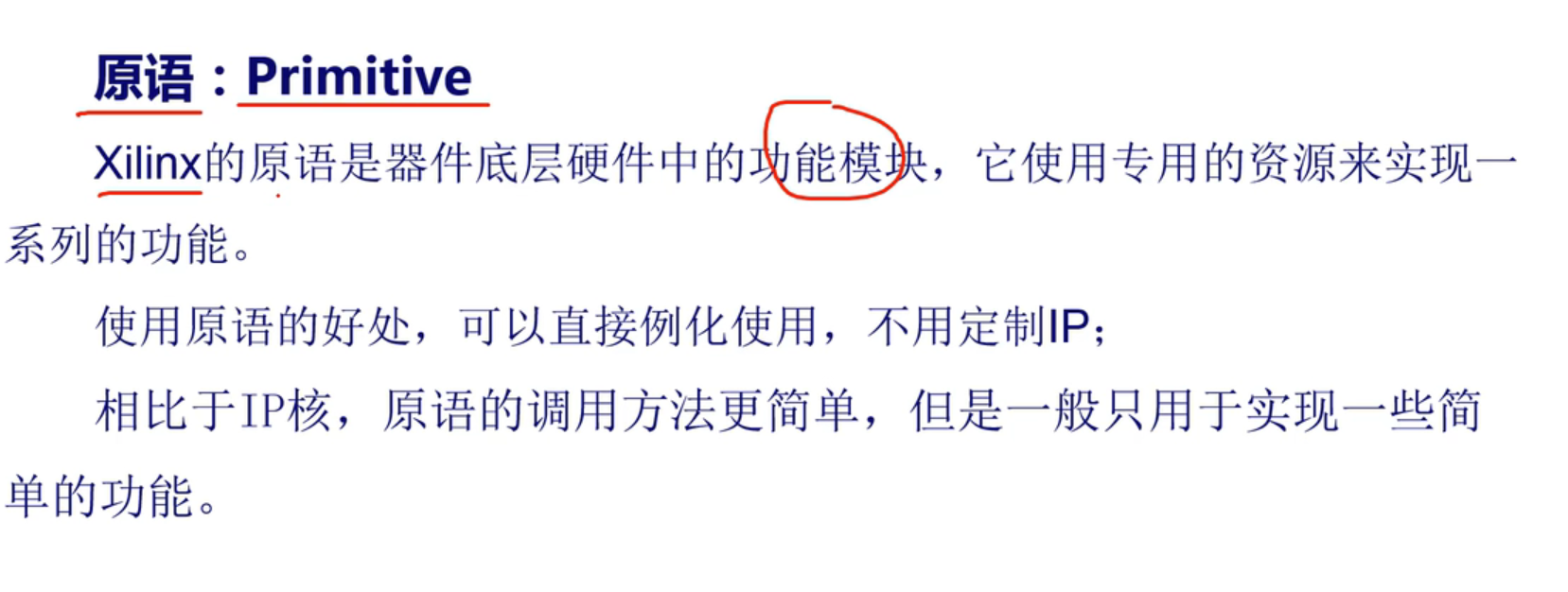

xilinx的原语的使用

在学习FPGA实现千兆网时需要GMII转RGMII,这就涉及了原语的使用,特此记录!

一、原语

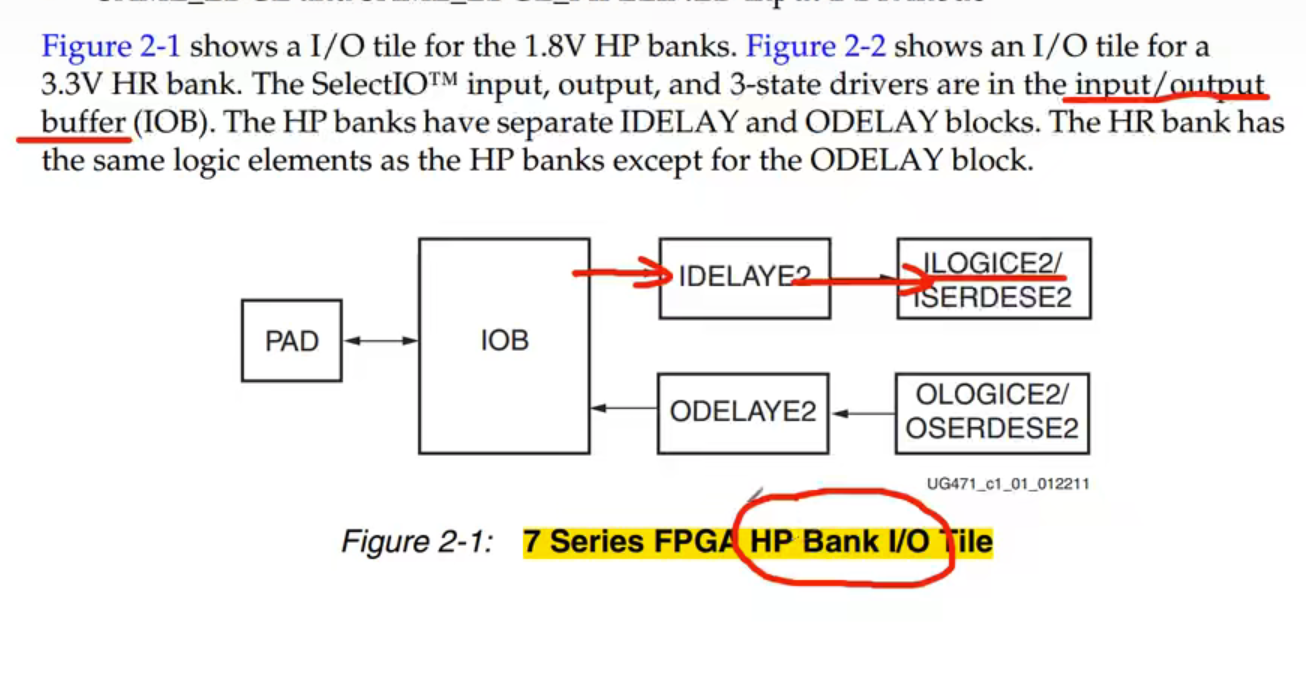

与RGMII接口相关的原语:

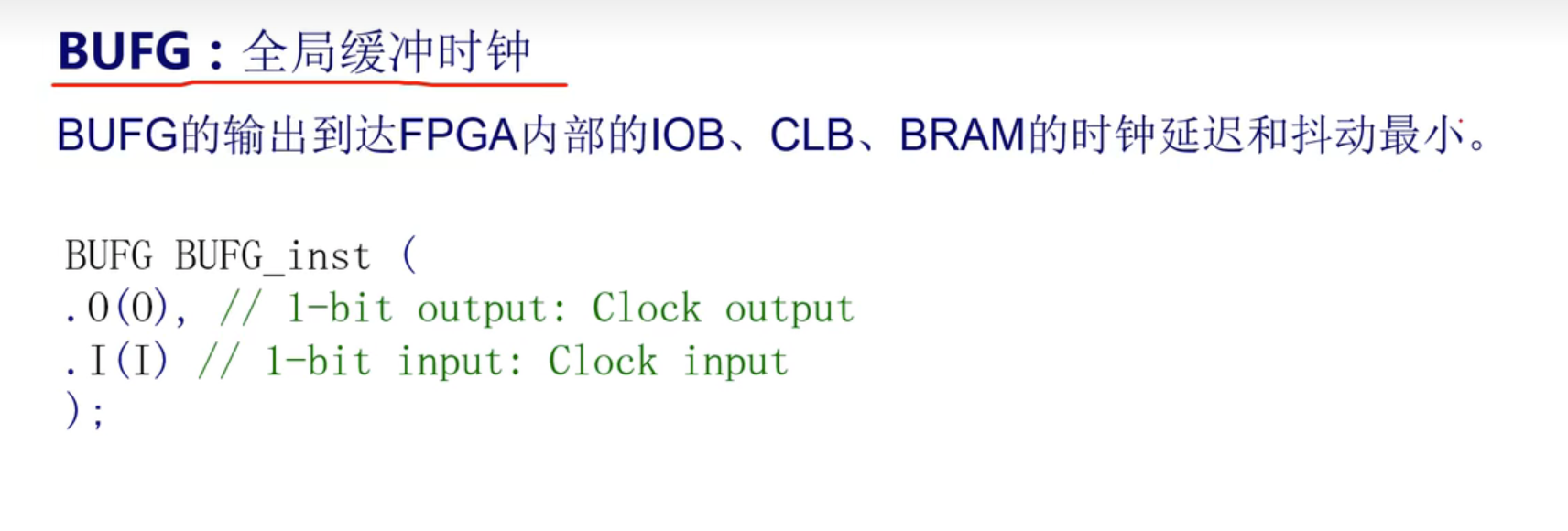

BUFG:全局时钟网络

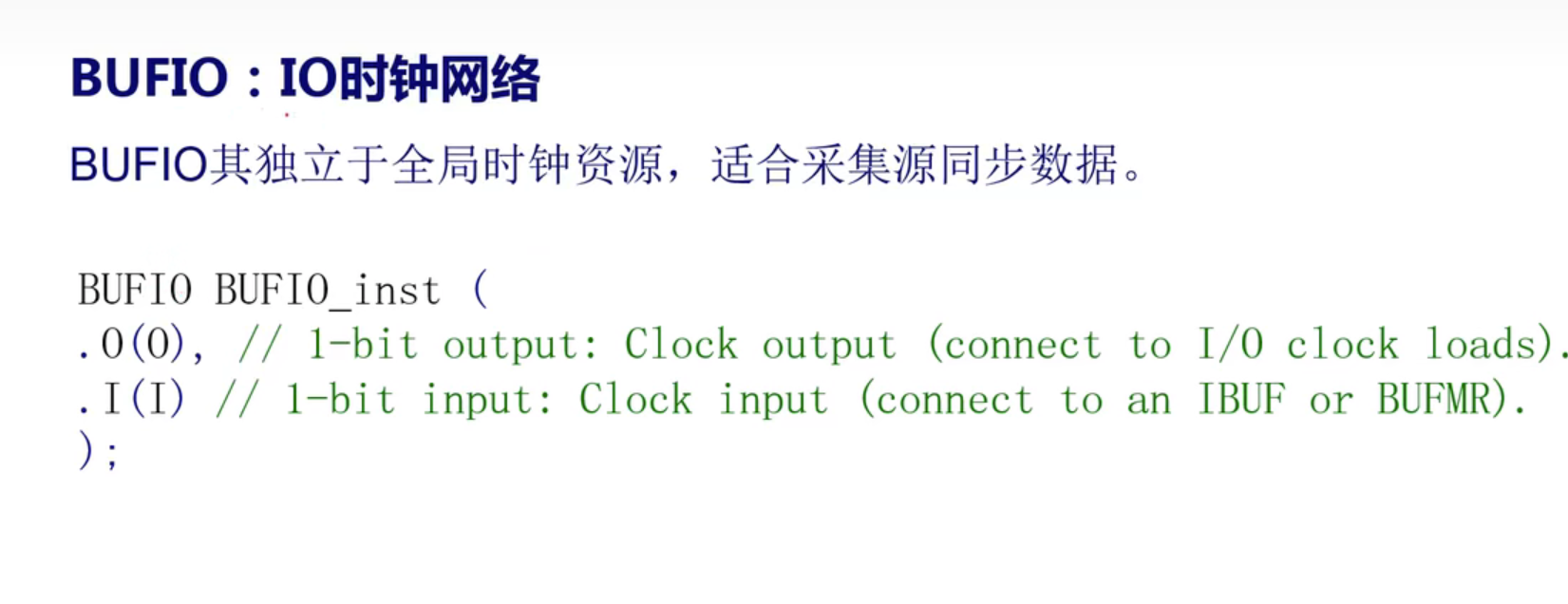

BUFIO:只能采集IO的数据,采集IO数据的时候延时是最低的

IDDR:双沿数据的采样,输出多位的数据

ODDR:输出,将输入的两bit数据在时钟的双沿进行输出,输出1位的双沿数据。

IDELAYE2和IDELAYCTRL:对数据进行延迟注:在ug472手册有详细的介绍

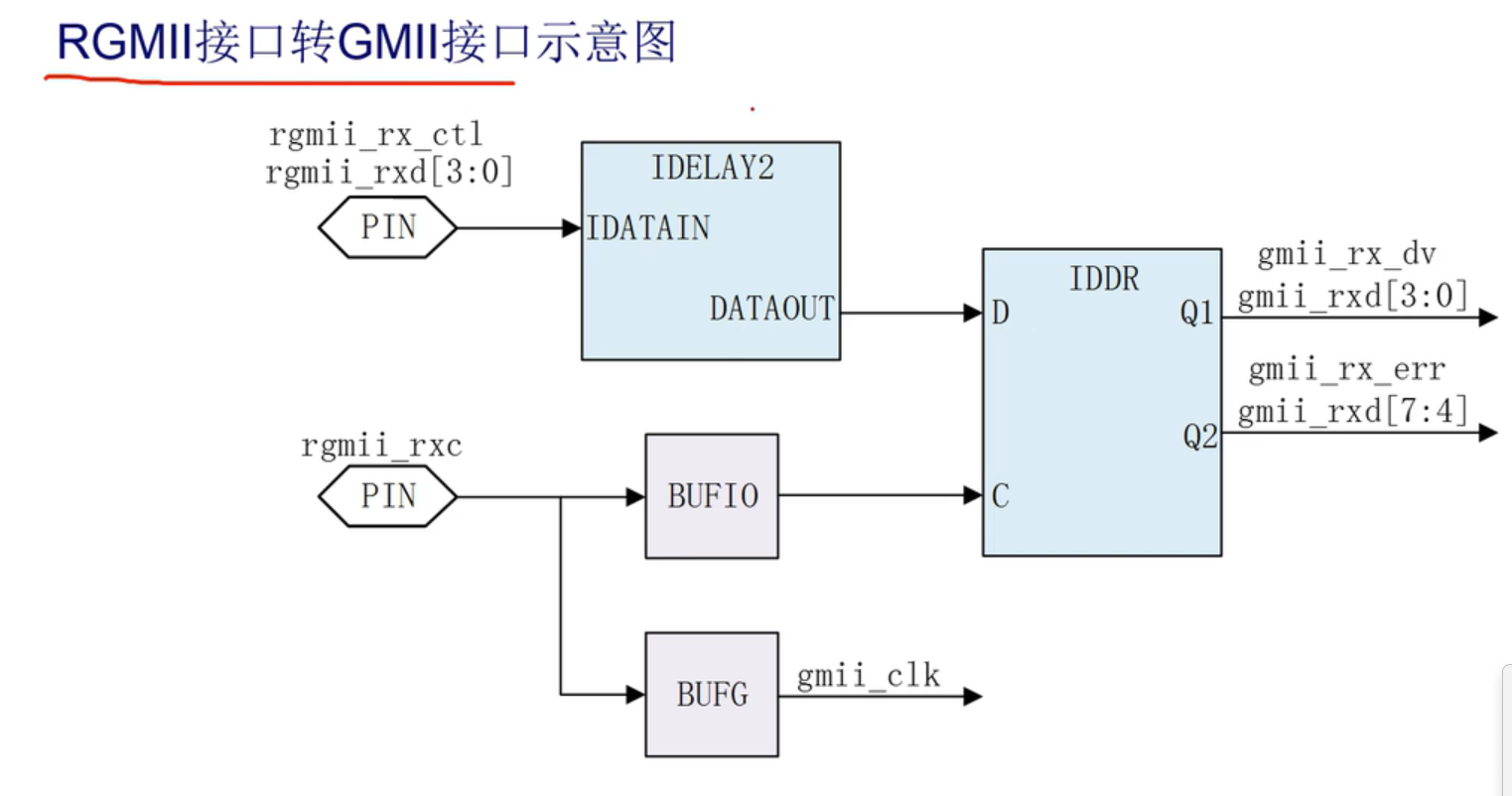

二、GMMI和GMII接口的转化

rgmii_rxc要连接到开发板上SRCC/MRCC类型的引脚上,否则编译错误,这些类型是专用的时钟网络

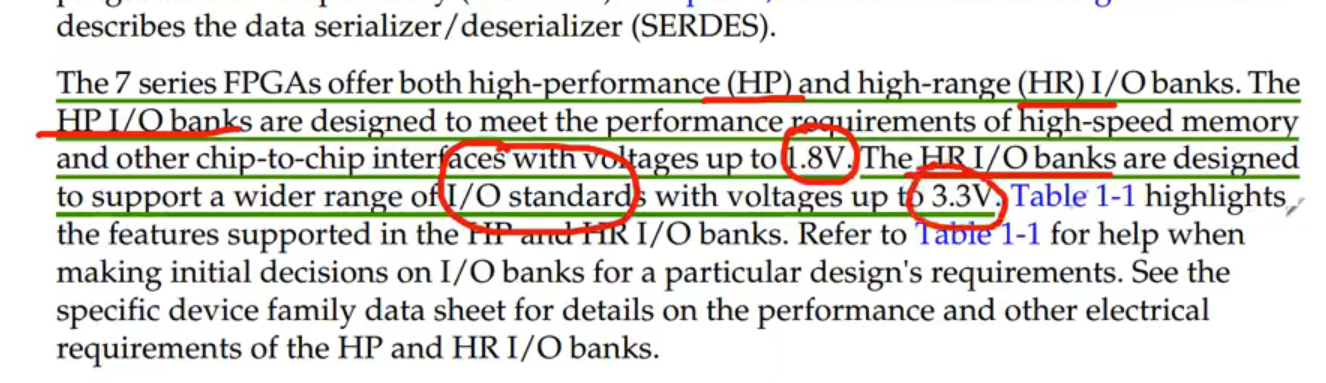

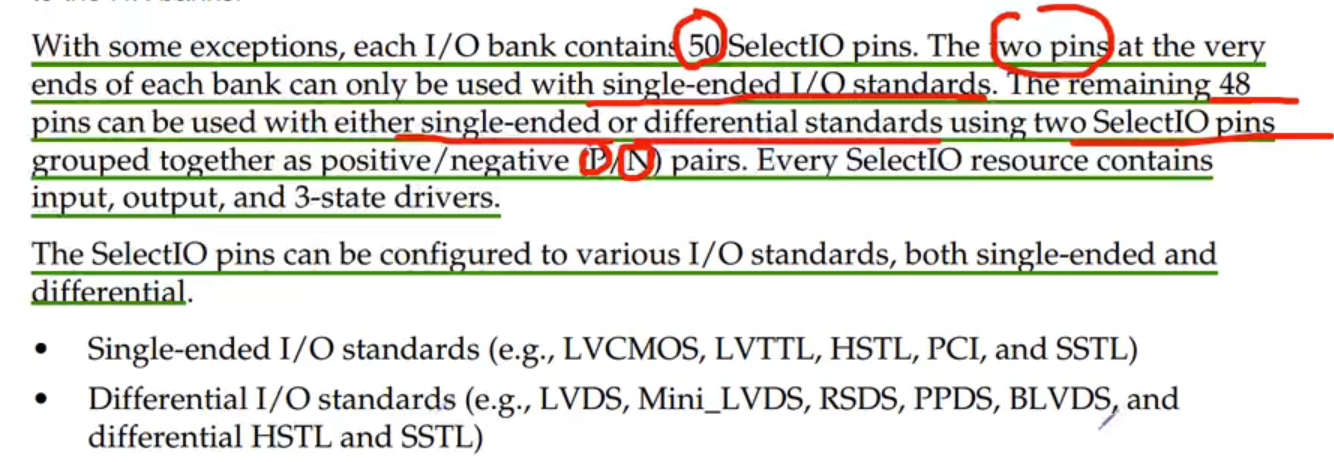

单端信号和差分信号:单端就是只用1跟线完成数据的传输,比如点亮led灯。差分信号就是需要两跟线来完成传输,优点:传输距离远,抗干扰强,更文稳定。

单端信号支持的电平标准:LVCMOS、LVTTL、HSTL、PCI、SSTL。

差分信号支持的电平标准:LVDS 、Mini_LVDS,RSDS,PPDS,BLVDS,differential HSTL and SSTL。

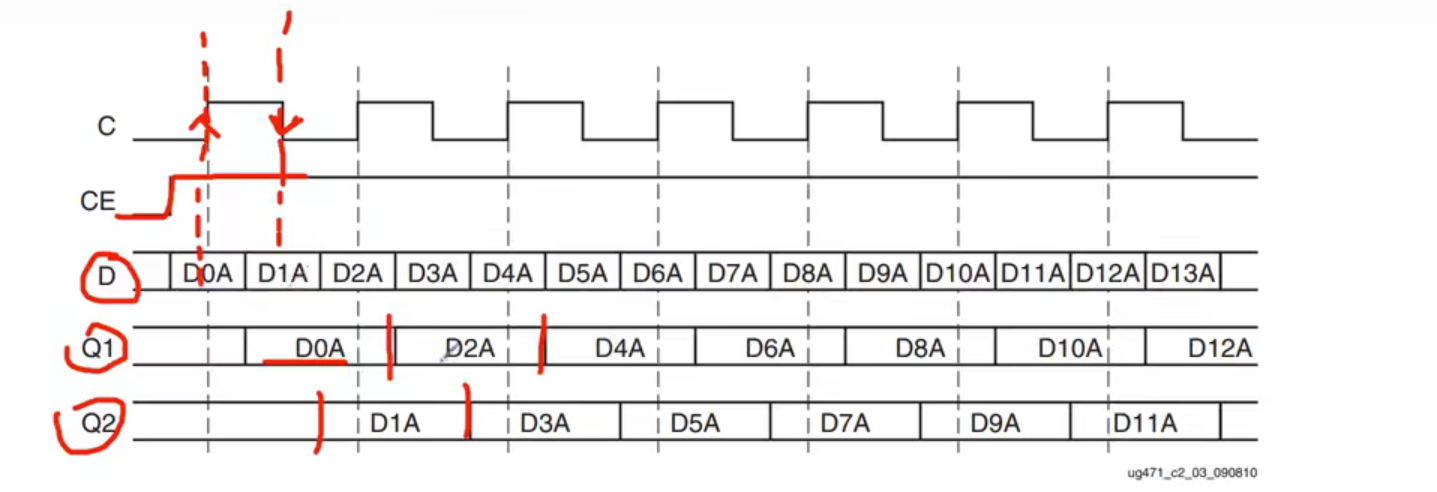

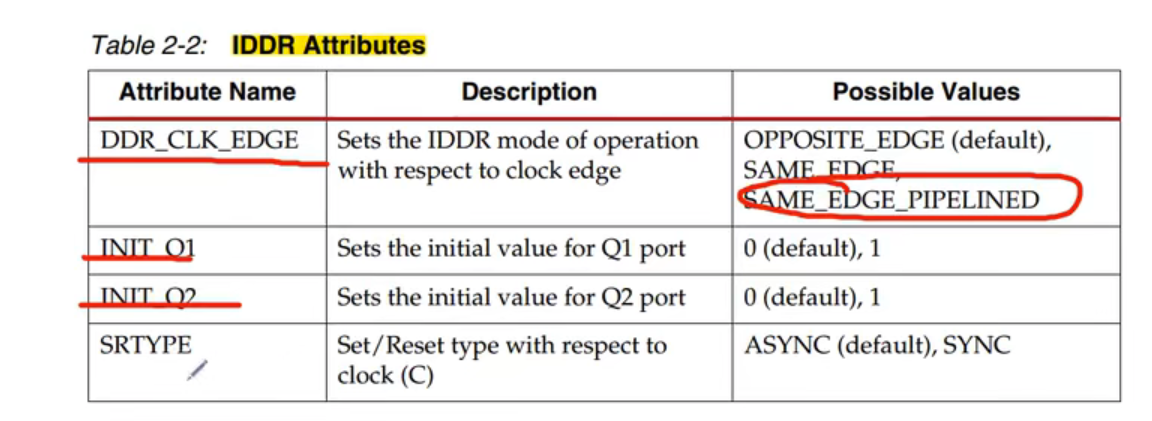

IDDR有三种模式:

- OPPOSITE EDGE mode

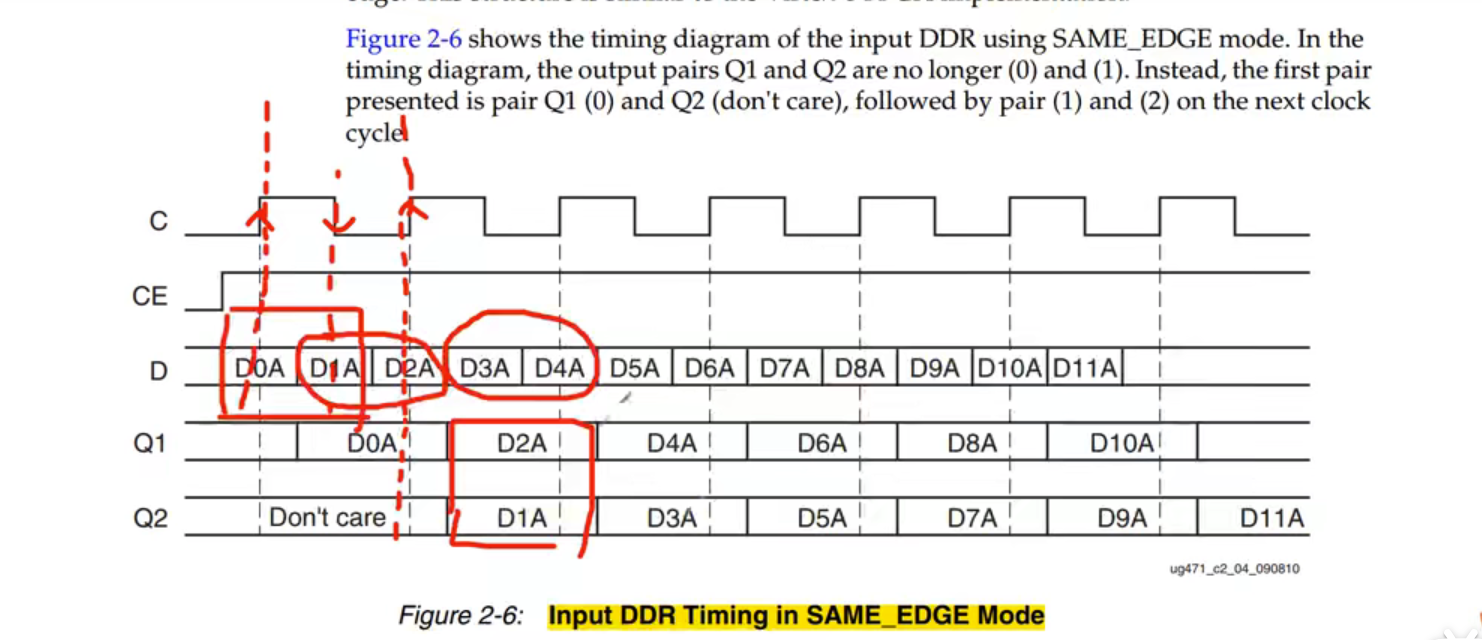

- SAME EDGE mode

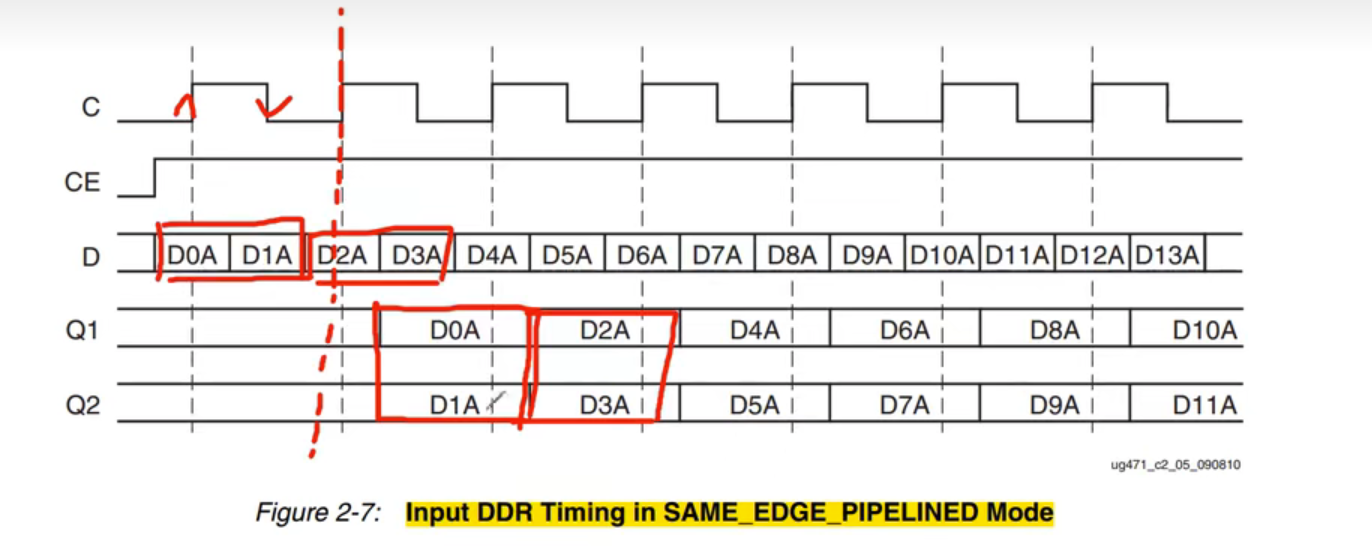

- SAME EDGE PIPELINED mode(使用比较多)

三种方式都是在时钟的上升沿和下降采集数据,不同的地方是对数据的输出方式不同。

1)OPPOSITE EDGE mode,双沿采样时序图:在时钟的上升沿和下降沿对一位的数据D进行采样,通过Q1和Q2进行输出。输出的数据Q1和Q2有相位差。

2)SAME EDGE mode模式:

3)SAME EDGE PIPELINED mode

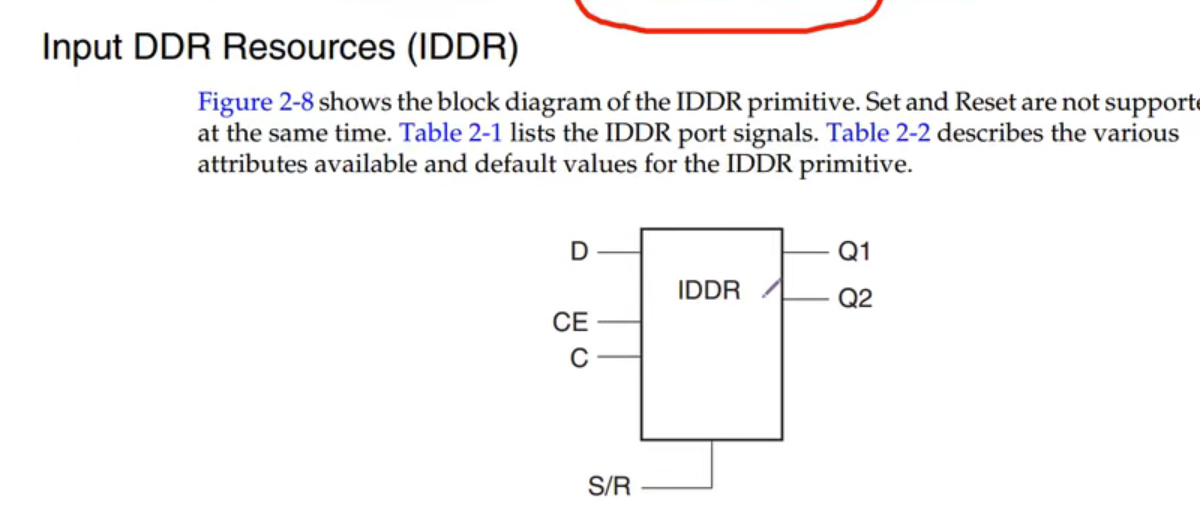

IDDR的示意图:

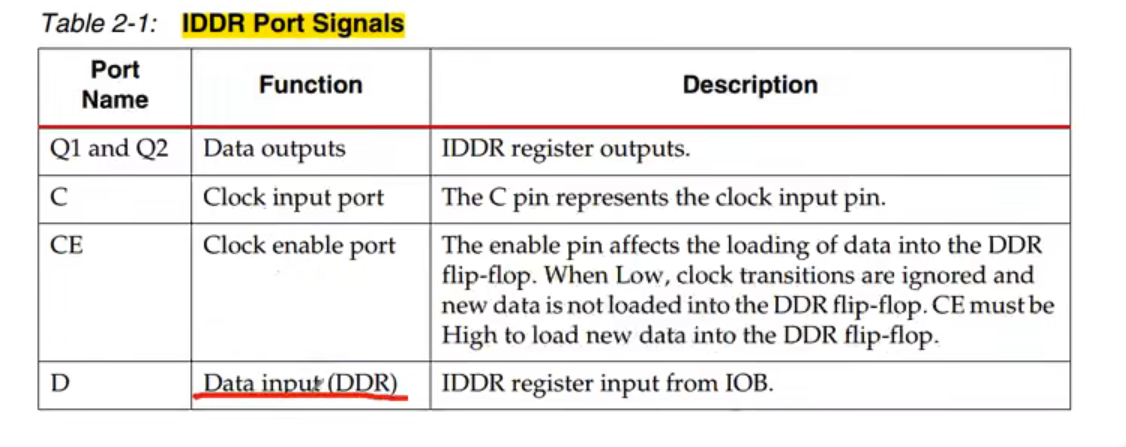

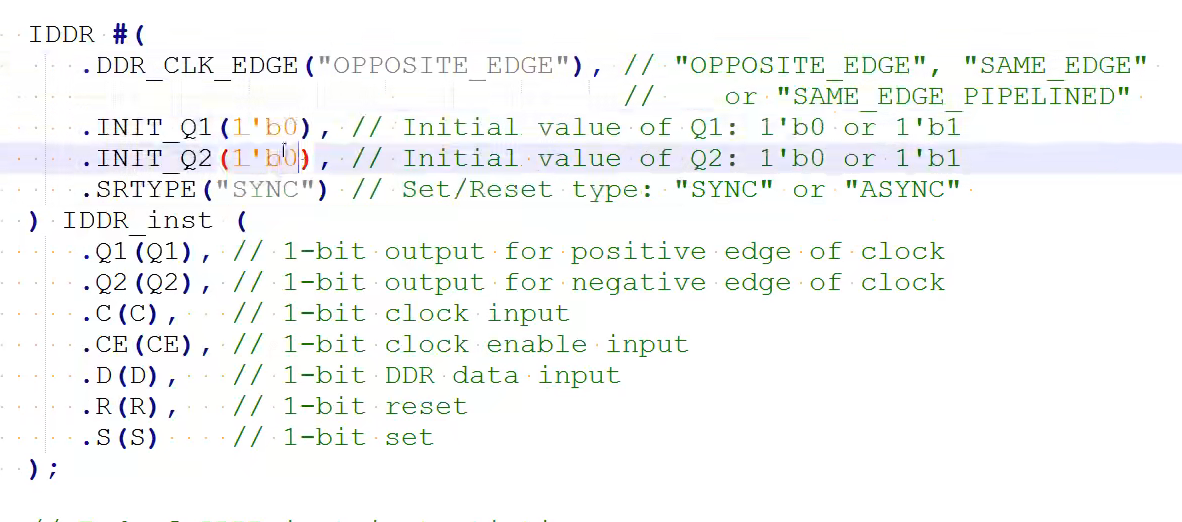

IDDR引脚的含义:

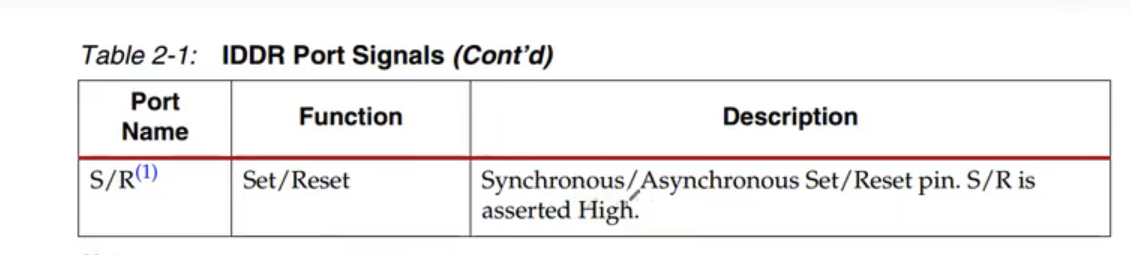

IDDR置位和复位的引脚:高电平有效

IDDR参数设置:

IDDR原语:

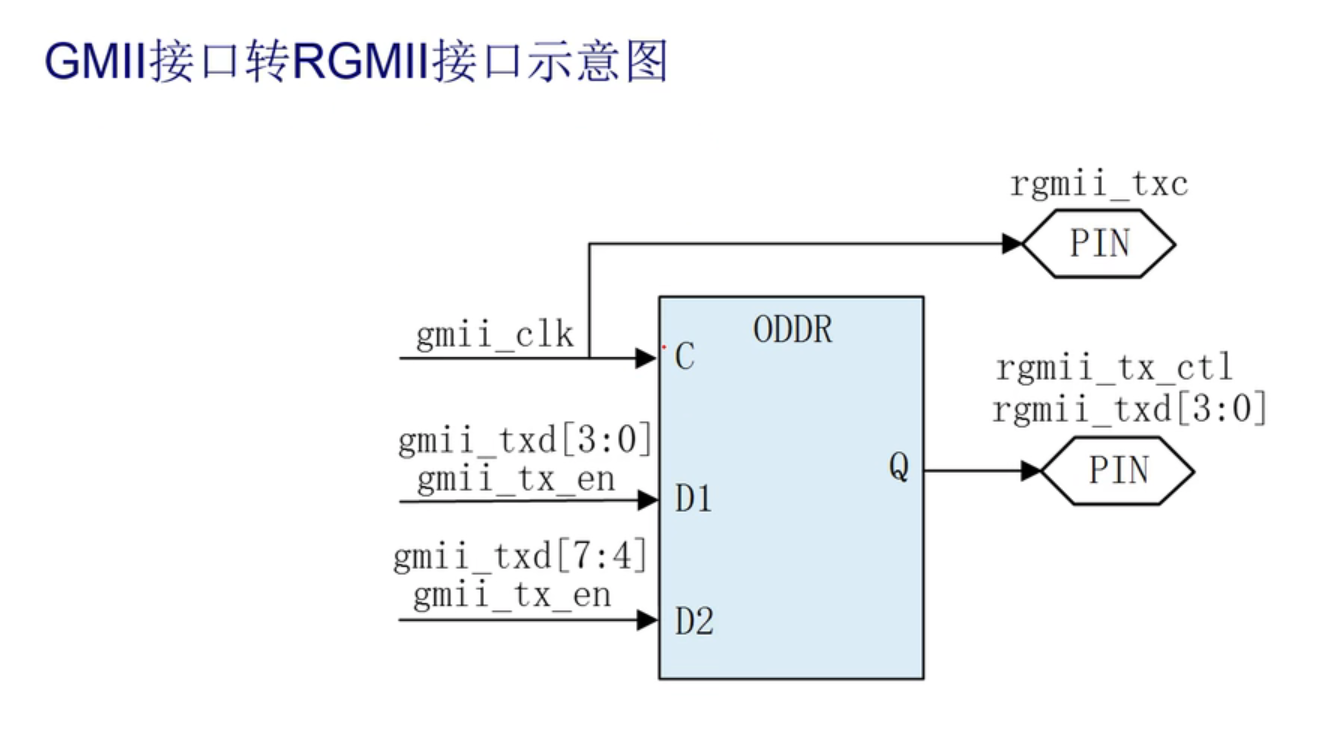

四、ODDR的两种模式:

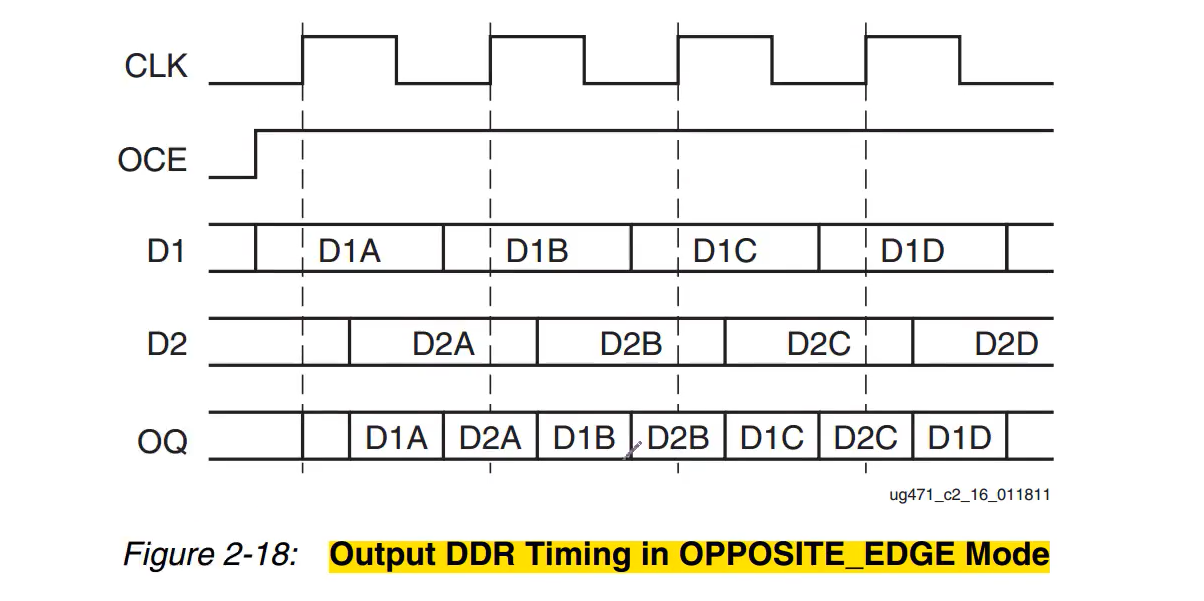

1、OPPOSITE EDGE mode

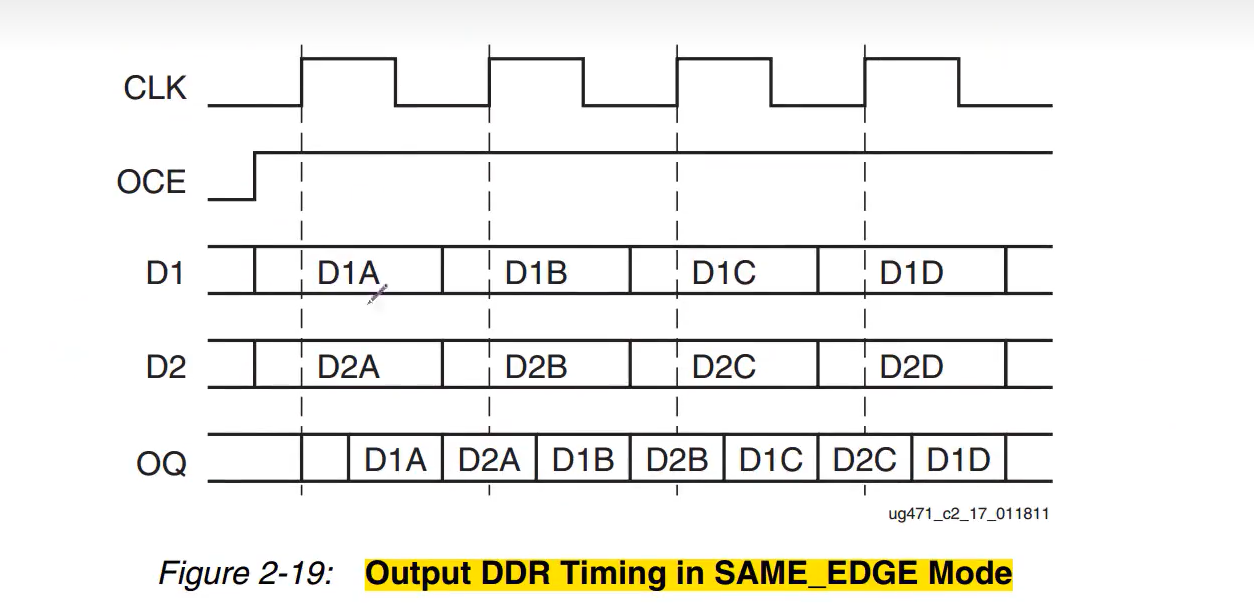

2、SAME EDGE mode

1)模式1:OPPOSITE EDGE mode。输入的两bit数据D1,D2转成1bit数据OQ的输出。输入的两位数据有相位的偏差

2)模式2:SAME EDGE mode。输入的两位数据无相位的偏差

(常用这种模式)

(常用这种模式)

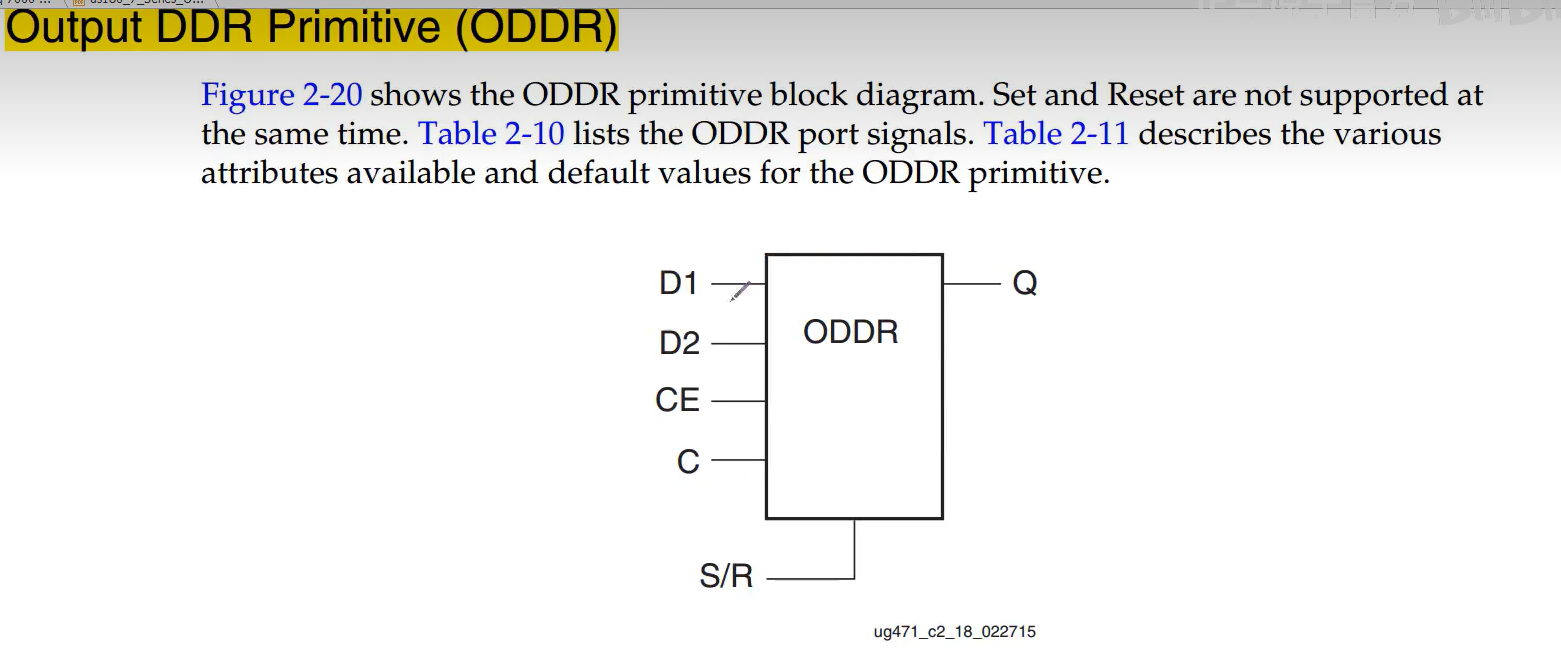

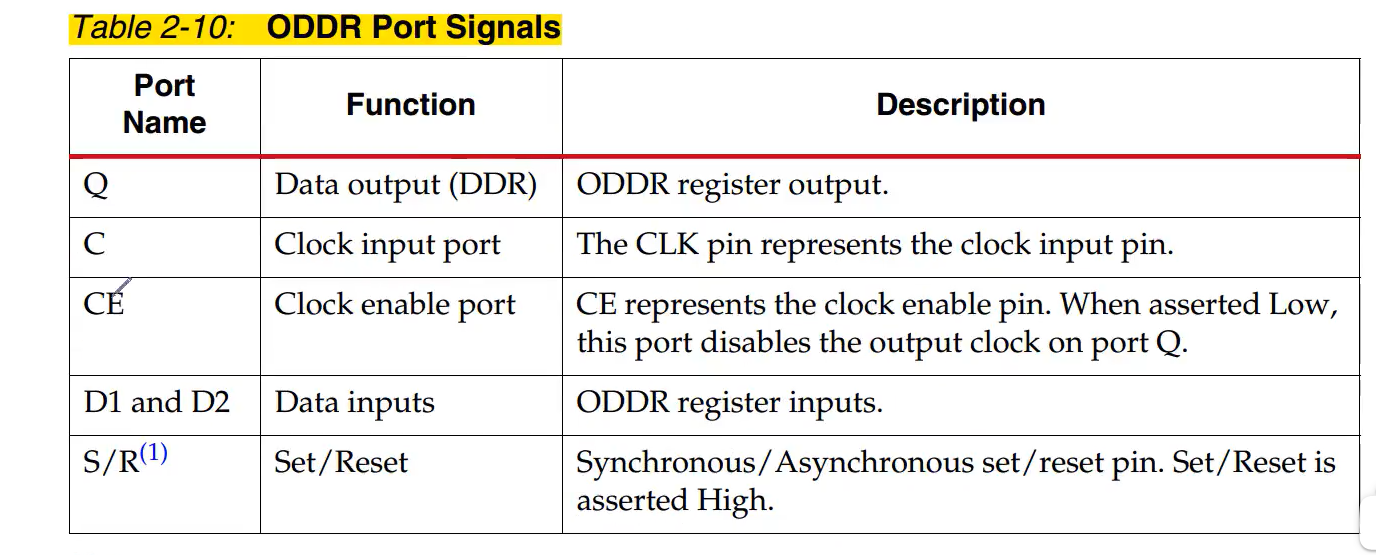

ODDR原语的框图和端口介绍

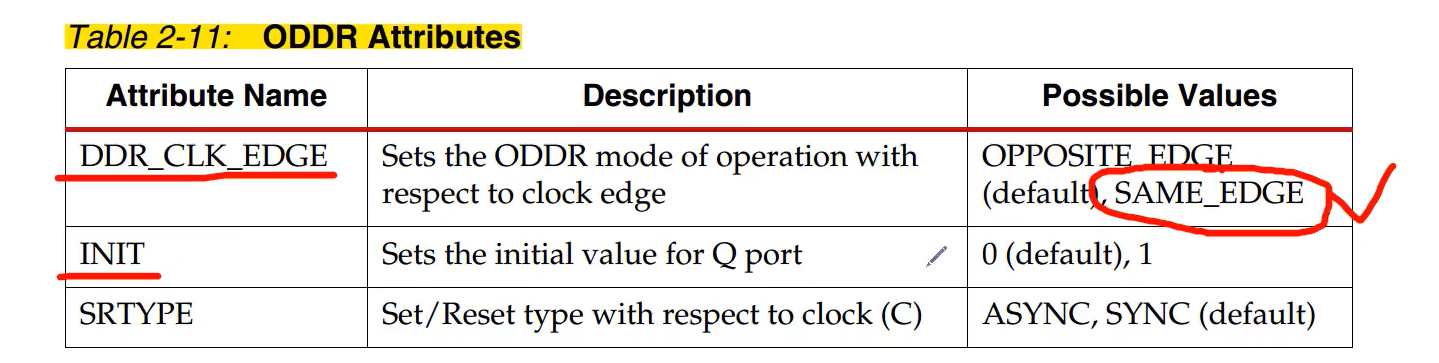

ODDR参数设置:

--晓凡 2023年10月2日于武汉书