大家在做RF上的PCB走线或者是车载相机的上走线的时候经常会听那些硬件工程师们说你这个走线一定要保证50欧姆的阻抗匹配啊,还有就是记得加粗走做隔层参考。

有的公司的EE硬件同事会很贴心的把RF走线的注意事项给你备注在原理图上或者是layoutguide上,遇到这样的EE同事的画那就好好珍惜吧,毕竟这么负责人的好男人不多了。列如,江湖流传一个消息说某个芯片设计公司的项目组中有些EE说这个是最终的原理图的了,不会再去改了,结果投板前改了十几个版本,Layout工程师不得不使用996的工作时间去赶进度了。所以说以后大家遇到这样的EE同事说的话,你也就听听就好了,千万可别当真啊,毕竟男人的嘴,骗人的鬼。小编我也不是故意踩低我们这个行业的EE同事,毕竟还很多设计公司的EE还是做事情负责的居多一些,懒散的少一些吧。

好了,我们言归正传。本期小编我主要给大家分享我最近做项目的时候遇到的一个问题,小编我最近做了一个我们公司乌克兰分部的一个板子,他们那边的Layout工程师由于忙着参加战争,这个板子也就直接扔给我们上海这边做了。小编我要不是看在之前的乌克兰大胡子的面子上我就直接拒绝了,想想还是为了两国的与友谊吧咬咬牙就接了这个烂板子了,再加上今年整个行业又那么卷,能有新的项目做就不错了,哪能挑肥拣瘦啊,而且小编我没有能力去躺平。

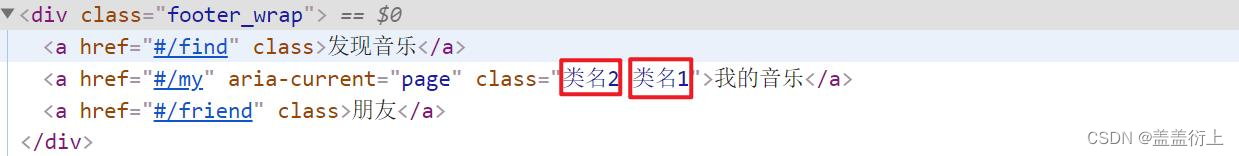

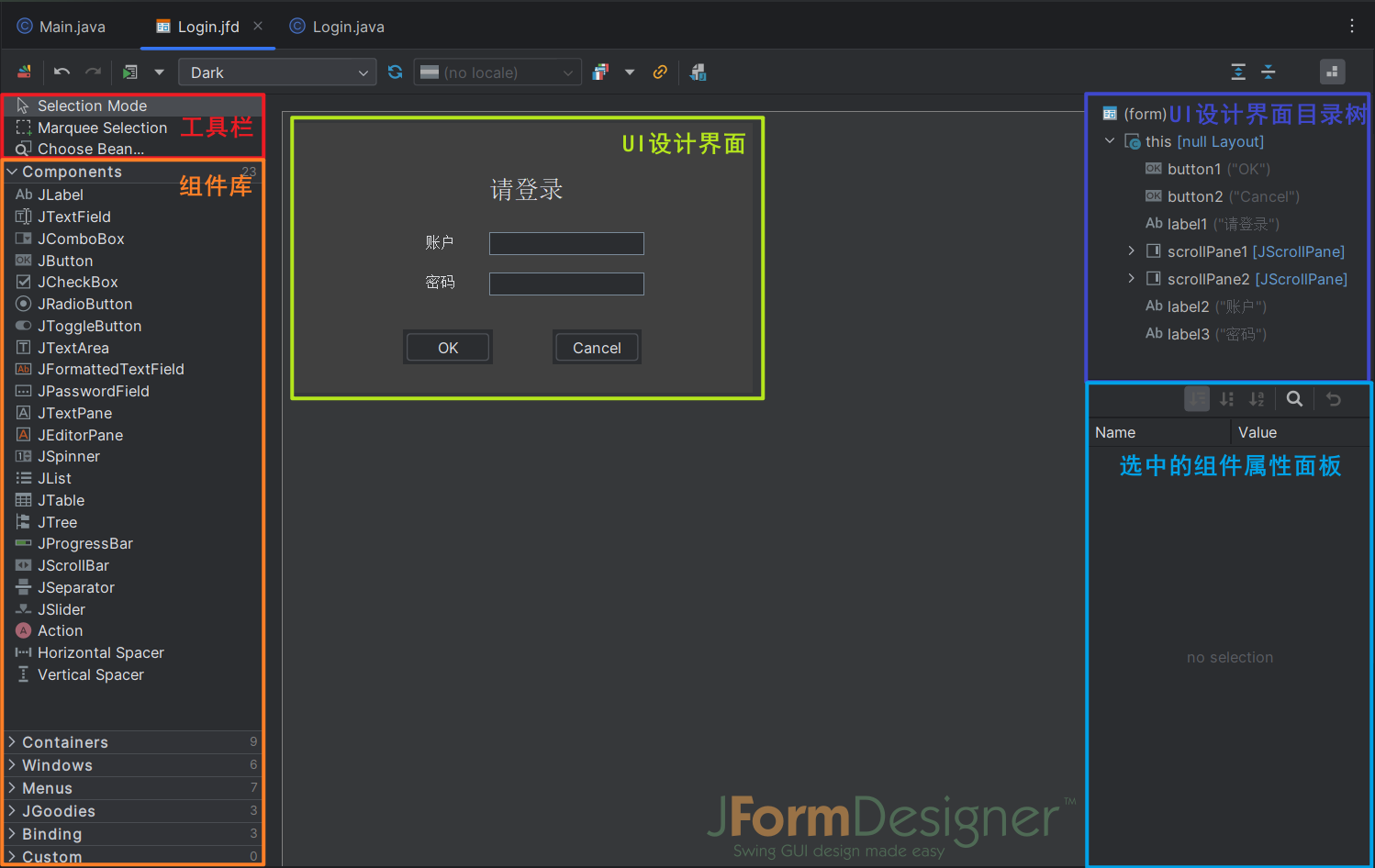

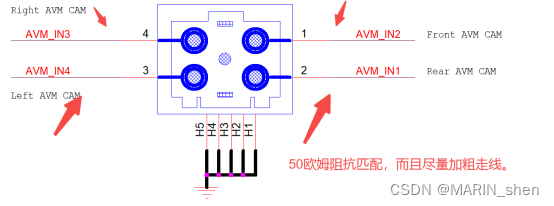

问题的主要是板子上有一个RF接口,上面也有EE同事备注的一些走线的要求:

在射频天线接口的电路设计中,为了确保射频信号的良好性能与可靠性,在电路设计中建议遵循以下设计原则:

1、应使用阻抗模拟计算工具对射频信号线进行精确的50 Ω 阻抗控制。

2、与射频引脚相邻的地引脚不做热焊盘,要与地充分接触。

3、射频引脚到射频连接器之间的距离应尽量短,同时避免直角走线,建议走线夹角保持为135°。

4、建立连接器件的封装时,信号脚需与地保持距离。

5、射频信号线参考的地平面应完整;在信号线和参考地周边增加一定量的地孔可以帮助提升射频性能;地孔和信号线之间的距离应至少为2 倍线宽(2 × W)。

6、射频信号线必须远离干扰源,避免和相邻层的任何信号线交叉或平行。

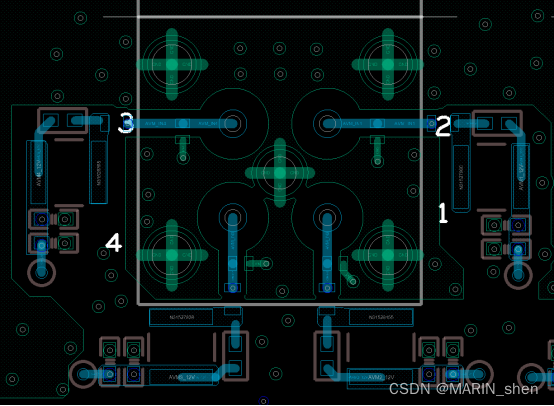

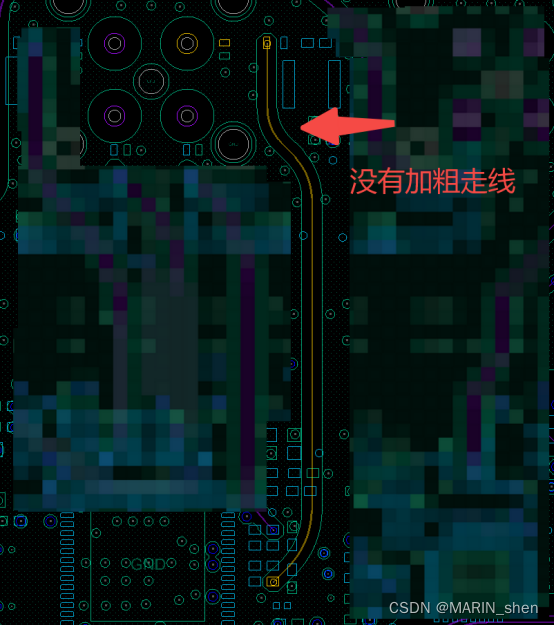

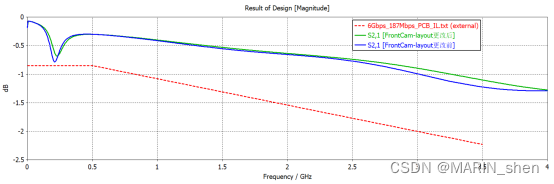

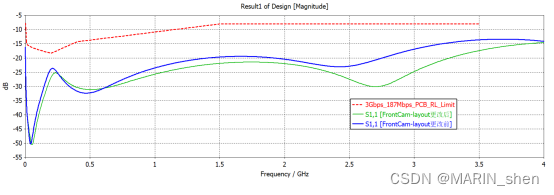

这个RF走线的设计不同的项目可能会稍微有一些不同吧。还有一些布局之类的要求等。这次小编我主要分享是一个RF走线的观点就是:RF走线在满足50欧姆的阻抗匹配的前提下,是直接走线用表层微带线按照正常的线宽(5-6MIL左右,不过这个线宽还是具体看不同板子的板厚和层叠情况来定的)走还是加粗走线做隔层参考好一些呢?我也问了旁边的EE同事马萨佗罗夫斯基,他说按照他以往的设计经验的话,要是这个信号有电流消耗比较多的话,就加粗走线吧,做隔层参考的那种50欧姆阻抗匹配的做法;没有太多的电流损耗的话就按照正常的5-6MIL的线宽也是可以的,毕竟我们之前的项目中确实有走线没有加粗而且还是走线在内层了。

而且这个信号我们也是让仿真同事做了信号完整性能仿真,优化PCB设计后也是是满足要求的。

我之前也是这样认为的,不过我心中还是有个疑问就是加粗仅仅就是为了信号的载流吗?这个时候测试的同事吴亦凡说你之前的不是有看到过一篇高速先生写的文章,而且你当时还让我们帮忙转发朋友圈啥的,那个讲的不就是关于信号线加粗走线的一些问题吗?小编我在此推荐一波高速先生这个微信公众号,这个上面有很多的优质文章,尤其是我们做PCB设计的更加应该多去看看的。

文章的链接如下所示:

线宽变大,损耗变小;线宽无限大,损耗无限小?------高速先生![]() https://mp.weixin.qq.com/s/GM_-ppNzNRp_6bXEs3lMbg

https://mp.weixin.qq.com/s/GM_-ppNzNRp_6bXEs3lMbg

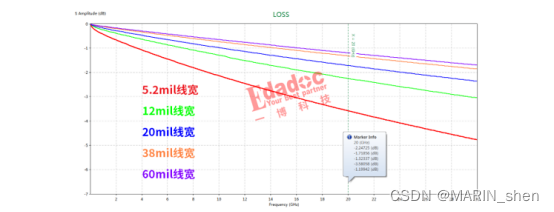

主要讲解的就是在满足信号线阻抗的前提下,其他的条件都不变的情况下,传输线的线宽越宽,传输线的损耗会越小,而且会一直是这个趋势不变,至于详细的讲解可以去阅读这个原文章。

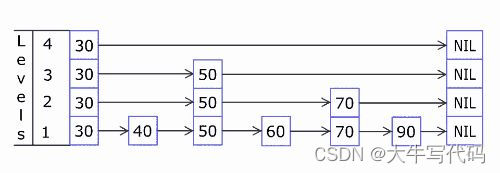

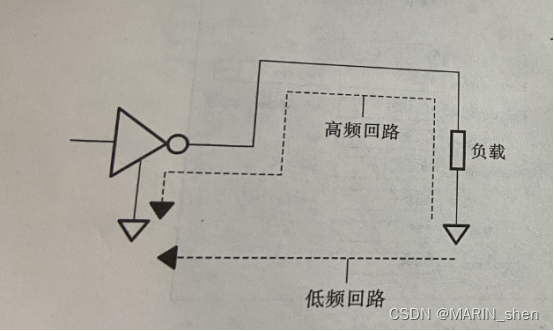

其实上面的文章牵扯到一个传输线的知识点就是传输线的损耗之一,导体损耗。大家都知道我们传输线并不是那种理想的零阶或者是一阶模型,因为正常的一阶模型是一个无损的理想模型,电感和电容是不消耗能量的,但是实际中我们的传输线是有损耗的,其主要的损耗来源为导体损耗的介质损耗。其中导体损耗顾名思义就是有导体本身的电阻产生的损耗,当电流流过导线的电阻的时候就会产生损耗的。在信号传输的时候,电流一般都会沿着电阻的最小路径走的。低速的信号的传输路径一般都是从source端传输到负载端口,然后沿着GND平面返回到驱动端口(source端)。返回电流一般会沿着最小电阻路径回去,而且它的的电流密度和和路径上的电导师相对应的。

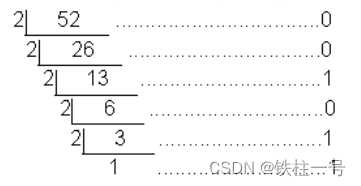

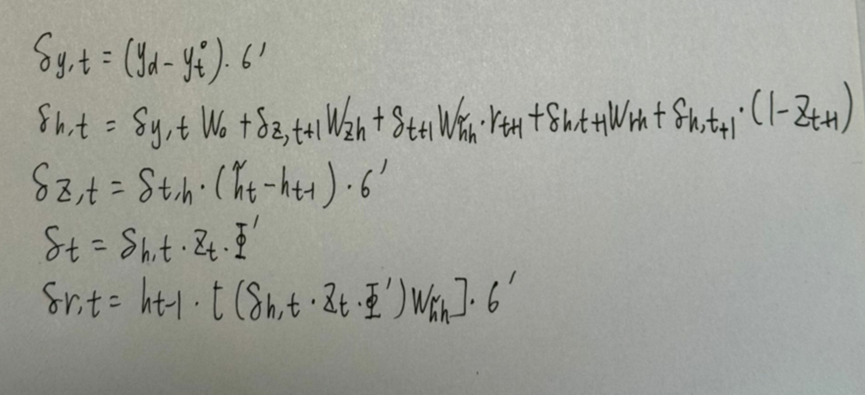

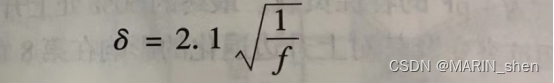

随着频率的升高,电感的感抗占据了主要地位了,这个时候电流就会找一个电感最小的路径回去了。关于趋肤深度的公式如下所示:

其中,δ表示为集肤深度(单位为μm),F表示为正弦波频率(单位为GHZ)

在这个趋肤效应下,信号能够感受到的电阻取决于导线传输电流的有效横截面积,这个真实的横截面积就是电流所流过的的面积,如果电流仅流过导线的下半部分,则导线的电阻近似可以看作:

其中,R表示的线电阻,(单位为Ω),P表示的是导线的体电阻率(单位为Ω·in),LEN表示的是线长(单位为in),δ表示为集肤深度(单位为in)。

那么问题就来了,我们应该如何减少电感呢?

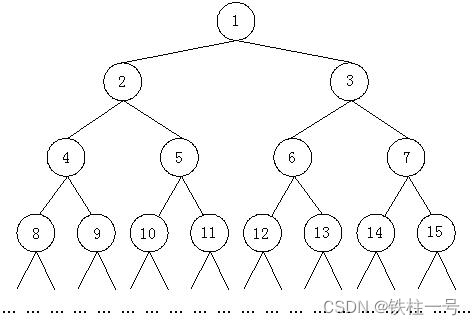

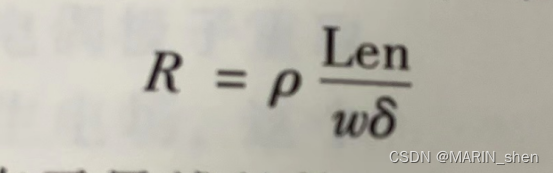

导线中的电流都尽可能地扩展开,以使得导线的自感最小。同时导线中的反向电流尽可能地挤进,这样就可以使得信号路径和返回路径之间的互感变的最大了。这个也是我们经常说的趋肤效应了。下图所示为10MHZ的正弦波在微带线和带状线中的电流分布

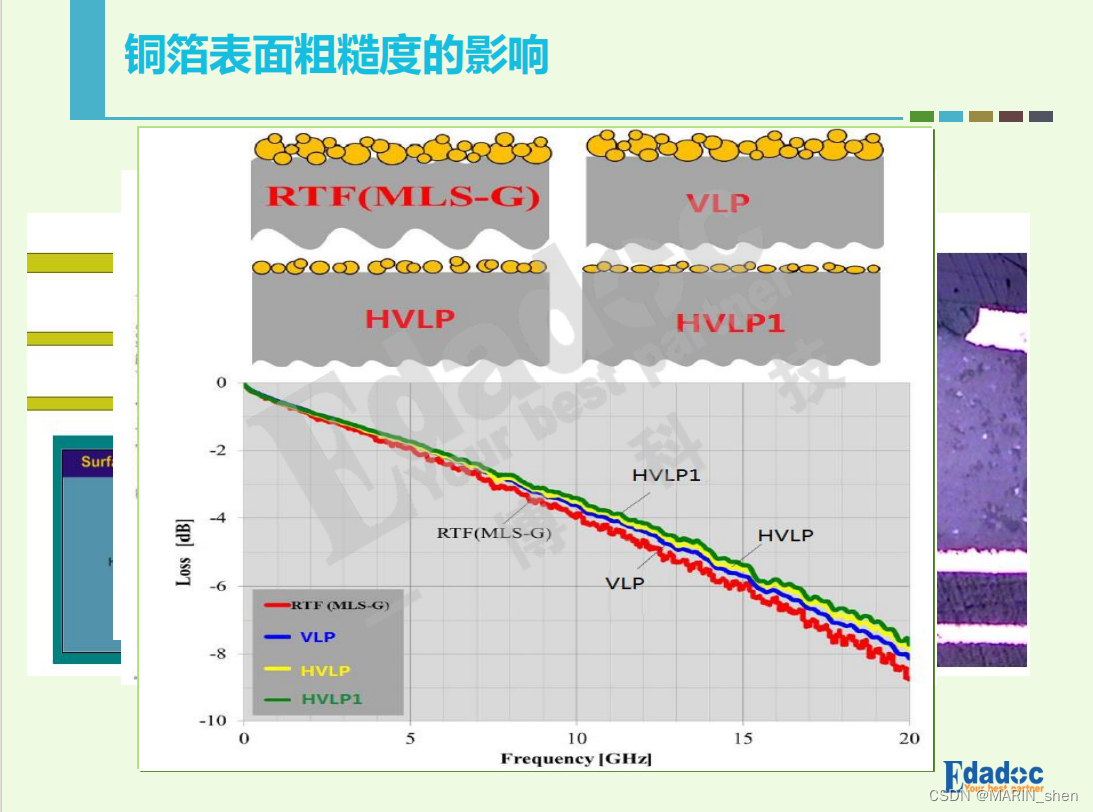

导体电阻带来的损耗就是电流电阻时候的损耗,由于电阻随着评率的增大而增大,所以说损耗也会随着评率的增大而增大。于F的1/2的次方正相关的。还有一个就是铜箔表面的粗糙度了,有STD,HVLP等不同类型的。

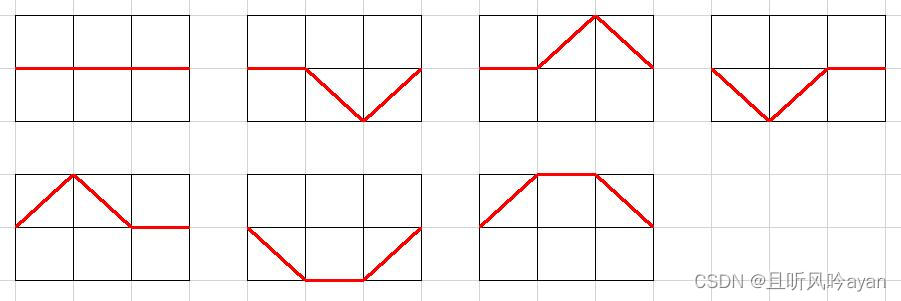

其实在其他条件都一样的的前提下,加宽走线就是为了改善PCB走线上的导体损耗,再去细分的话就是导体损耗分为改善去趋肤效应和铜箔粗糙度,而我们这个做法其实就是主要去改善PCB走线上的趋肤效应带来的损耗。

(图片来自一博研讨会课件分享)

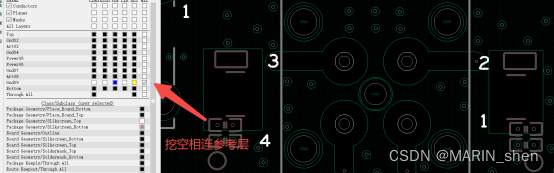

总而言之,类似RF这样的射频走线我们在满足其阻抗匹配的前提下,PCB的走线还是加粗一些做50欧姆的这个做法比较好一些,这样就可以减少信号在传输路径上的一些损耗了。但是记得PCB走线也不是无限制的加粗就好,因为越往后面就改善的量级不多了,而且你的PCB的布线空间也是有限的。就按照隔层参考挖空就好了,当然这个也是看你的板厚层叠了,有的是需要挖空两层才满足相应的50欧姆的阻抗匹配的。以上就是本篇文章的所有分享了,记得点赞收藏加关注啊,帖子们。