分享使用Virtuoso GXL Custom Digital Placer(VCP) & Space-based Router(VSR)工具进行基于纯数字Standard-Cell布局布线的操作流程。

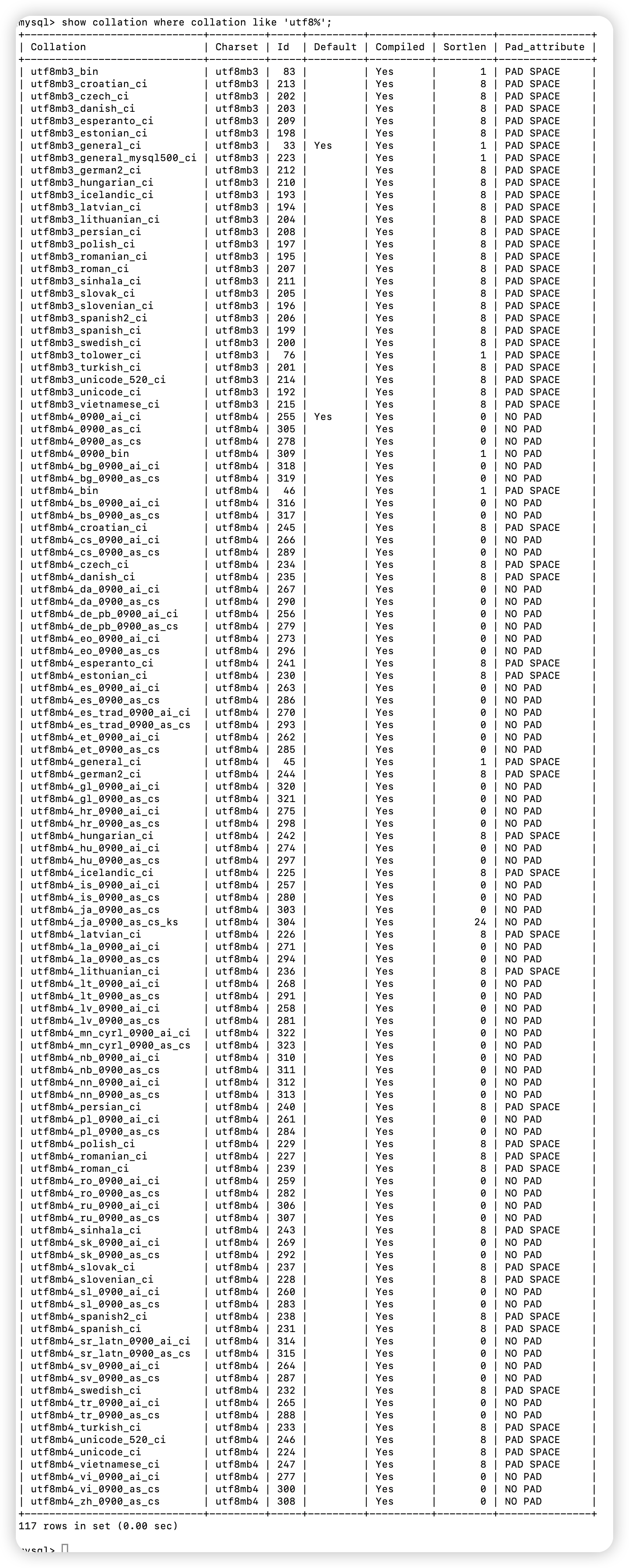

VCP&VSR演示的工具版本信息:

Virtuoso: IC6.1.8 GXL

GPDK: GPDK045_v_6_0

Standard-cell: GSCLIB045_all_v4.4

⚠️运行VCP&VSR需要有GXL Lisence:

一、准备工作

在VCP&VSR流程中使用到的标准单元,无论是PDK厂商提供还是手工绘制的,都需要满足下面几点要求:

1)使用某个层次画出单元的界限尺寸,以此来定义单元的摆放标准。 比如使用PRBoundary / BORDER / STD_B等层次。

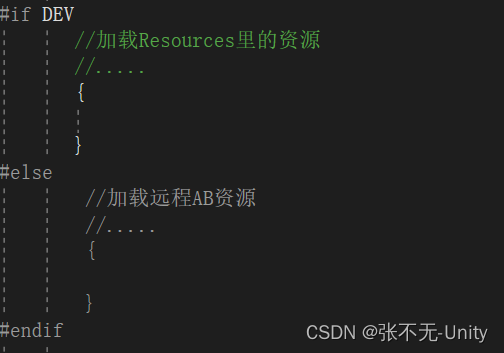

⚠️如果使用了Virtuoso默认层 PRBoundary 以外的层次,需要修改 .cdsenv 文件中环境变量 vcpCellBoundaryLPPS 的定义:

layoutXL.placement vcpCellBoundaryLPPS string "BORDER"

(引号中的内容替换成实际的边框层次)

2)单元内部已经生成好所有的PIN,确认「Navigator」->「Pins」分类下存在这些物理位置信息。

⚠️在使用PDK的Standard cell library或人工绘制标准单元时,注意上面提到的几点条件是否满足要求。

除了标准单元的绘制要求外,工艺文件(techfile.tf)还应包括标准单元的基本定义,通过 siteDefs 定义库中最小尺寸标准单元的宽度和高度。 举例如下:

siteDefs (

scalarSiteDefs(

;(siteDefName type width height symInX symInY symInR90)

(gpdk045Site core 0.2 1.71 nil nil nil)

)

)

例如在我用到的 GSCLIB045 库中,以「FILL1」为最小单元,只需测量该单元 PRBoundary 层的宽度和高度填入即可。 其它工艺也可以通过*FILL*命名方式的单元入手测量尺寸信息。

(最小单元 FILL1 的宽度和高度信息 )

修 改完 te chfile.tf 工艺文件后,需要 重新载入文件才可以生效。 点击 CIW窗口 -> Tools -> Technology Fil e Man a ger,选择 「 Load… 」 :

📌上方截图的第三步③也可以不勾选「Select All」只勾选「siteDefs」然后选择「Merge」的方式进行更新。

二、运行VCP前的配置

下面,通过演示一个官方的案例来说明VCP&VSR流程的具体步骤。

📌公众号后台回复「VCP」可获取配套案例。

1)打开电路图 adcflash_therm2bin,菜单栏点击「Launch」->「Layout GXL」,在弹出的Startup Option对话框中选择「Create New」->「OK」

2)生成好版图后,在Layout窗口的菜单栏点击「Launch」->「Configure Physical Hierarchy…」进行CPH配置,这里主要是确认 Physical stop view list 先选择哪种view进行调用:

3)CPH编辑对话框默认打开的是 Hierarchy Configuration 设置,点击下拉菜单切换到「Component Types」:

配套的案例中 Component Types 这部分内容已经通过LAM文件的定义方式配置完成,所以我们不需要再去手动配置了。

📌如果你对创建的LAM文件感兴趣,可以在下面截图的路径中找到该文件:

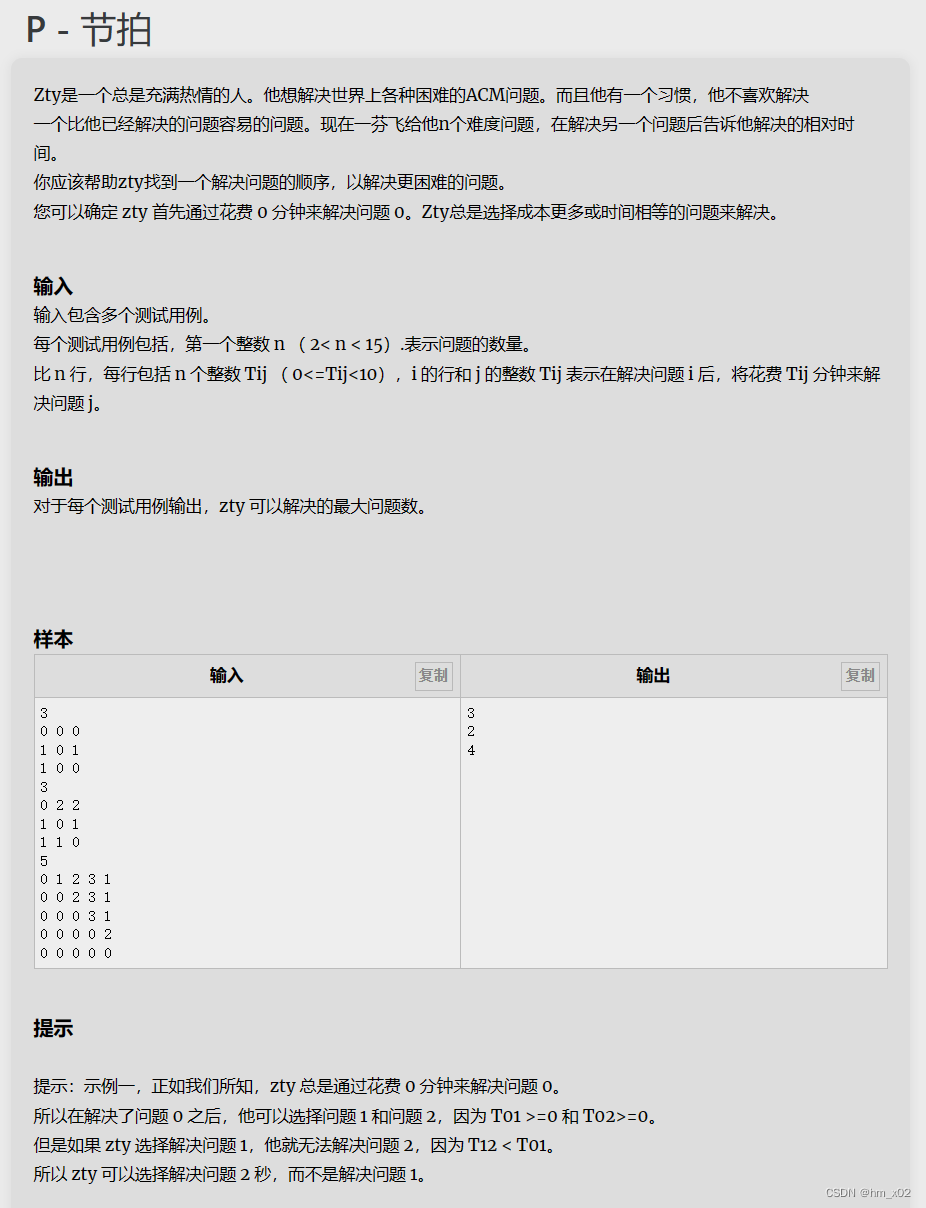

4)下面介绍 Component Types 初始状态下GUI界面的配置步骤。

4.1 在对话框中,右键点击「No component type」->「Show cells」勾选上「gsclib045」,显示标准单元库中未配置的所有单元。

4.2 从下方 Attributes 属性面板「Component class」的下拉菜单中可以看到,存在的 Component Types 都有哪些。 VCP主要按照「STDCELL」,「FILLER」和「STDSUBCONT」三个类型进行配置。

(展示的是Component class下拉菜单内容 )

回到 No component type 处右击,选择「Add Component Types…」将未配置的单元进行分类,下面演示创建分类 STDCELL 的操作步骤:

选中「STDCELL」在 Component class 的下拉菜单中选择「STDCELL」:

选中所有所属分类的标准单元右击,选择「Move cells…」

这样就完成了第一个Component Type创建,以同样的方式重复上面的步骤1~10,继续创建「FILLER」和「STDSUBCONT」

(Component Type —— FILLER )

(Component Type —— STDSUBCONT )

如果使用的是其他厂商提供的 Standard Cell Library,标准单元的命名可能各不相同。 比如这里的 STDSUBCONT 选择的Cell可能是以「TIE」命名的单元,需要注意一下。

5)完成所有设置后,点击「File」->「Save」,保存 physConfig view。

三、VCP的布局规划

1)通过Layout GXL的菜单栏,点击「Connectivity」->「Generate」->「All From Source」,开始生成版图:

2)在弹出的Generate Layout对话框中,注意不要勾选「In Boundary」选项:

4)菜单栏点击「Place」->「Custom Digital」->「Placement Planning」

5)在弹出的 Placement Planning 对话框中,Tap Cell子选项卡会列出之前定义为 STDSUBCONT 的标准单元,点击「Choose…」可以新增单元或移除单元:

6)Row 子选项卡可以设定行的生成,主要设置行的间隔和疏密程度等,可以根据实际的版图要求进行数值调整:

7)Create子选项卡可以选择现有的 PRBoundary 或指定 PRBoundary内的特定区域,来设定布局尺寸的大小。 选中「Placement Region」选项后,版图中的PRBoundary层会被高亮显示,可以通过「Draw」指定区域或者输入「Width/Height」信息来更新布局大小:

如果PRBoundary的尺寸太小,区域内无法放置所有标准单元的情况下,CIW窗口会有 WARNING 提示信息,我们可以通过调整PRBoundary尺寸来解决这个问题:

8)点击 Placement Planning 对话框下方的「Insert」,生成后的整体布局如下图所示:

如果需要取消本次规划的布局,返回 Placement Planning 对话框点击下方的「Delete」可以撤销操作。

📌Tips: 菜单栏点击「Options」->「Display」勾选「Row Name / Row Site」可以显示摆放行的信息。

四、VCP的自动摆放

1)菜单栏点击「Place」->「Custom Digital」->「Auto Placement」:

2)Auto Placer 选项卡的设置,可以参考下面几点建议:

2.1 Effort 选择「high」耗时长且有可能导致后续绕线失败,建议初期选择「low」模式进行调试;

2.2 勾选「Run Spacer Within Rows」选项可以提高绕线的成功率;

2.3 勾选「Insert Tap Cells」选项行内的标准单元之间会预留 Tap Cell 的摆放空间。 如果未定义STDSUBCONT Component Types,不要勾选此选项;

设置完成点击「Apply」开始摆放标准单元,完成时会有一个进度信息统计的弹出框:

如果希望重新设置以再次运行 VCP Auto Placement,可以点击「Floorplan」->「Reinitialize…」打开选项卡进行设置:

📌先选择「none」再勾选「Initialize instances」。

3)菜单栏点击「Place」->「Custom Digital」->「Insert/Delete Fillers」插入Tap Cells,行内剩余的空间将会被Tap Cell填满:

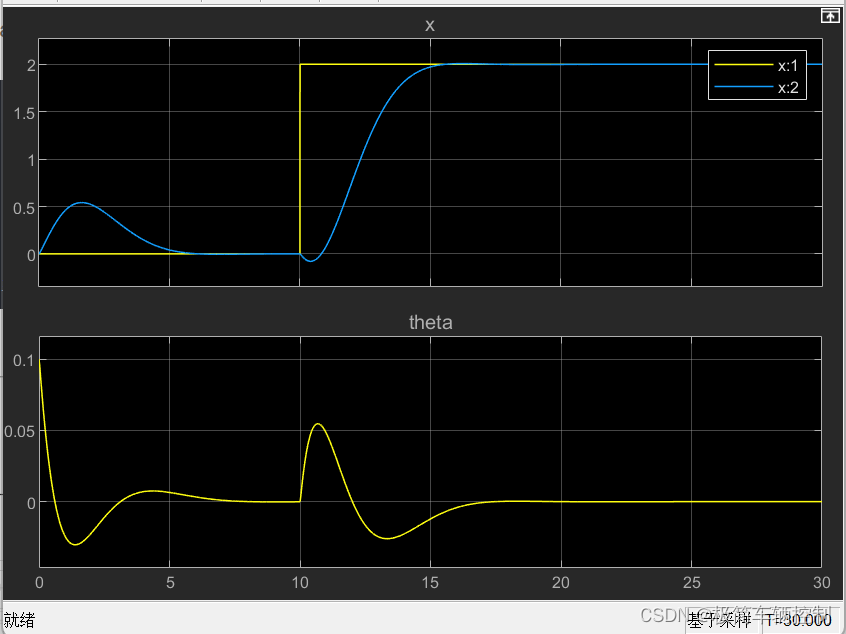

五、VSR的自动绕线

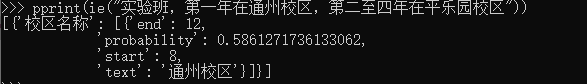

1)点击「Window」->「Assistants」->「Wire Assistant」来设置绕线规则。

1.1 这里我选择 M1~M4 作为绕线层;

1.2 Design Style选择「ASIC」;

1.3 最后点击 Route Net 旁的「ALL」按钮,或者先选中需要绕线的 Net 再点击「Selected」开始绕线程序;

绕线开始后,我们可以通过CIW窗口看到绕线的进程信息:

以上,供参考!

02 - LVS验证时Source端网表未定义SUBCKT

05 - 资源分享 | Cadence GPDK Downloads