一、System-Verilog

System Verilog的发展

SystemVerilog 的出现是为了因应日益复杂的数位电路设计和验证需求。虽然Verilog HDL 在早期的数位电路设计中得到了广泛应用,但随着技术的发展和电路复杂度的增加,Verilog HDL 在某些方面已经显得有些不足以满足设计者和验证工程师的需求。因此,有必要引入一种更强大、更灵活、更先进的硬体描述语言,从而诞生了SystemVerilog。

和Verilog的区别

Verilog

基本特性:

Verilog是一种高级的硬件描述语言,主要用于RTL(寄存器传输级)建模。

它提供了基本的建模结构,如模块、端口、线网列表、赋值语句、条件语句、循环语句等。

Verilog支持两种主要的描述风格:行为级建模(使用always块)和结构级建模(使用模块实例化)。

应用范围:

Verilog广泛用于数字电路的设计和验证,尤其是在ASIC(应用特定集成电路)和FPGA(现场可编程门阵列)的开发中。

它适用于简单的逻辑设计、复杂的微处理器设计以及PCB(印刷电路板)级别的设计。

局限性:

Verilog在设计大型、复杂的系统时可能会遇到一些限制,特别是在验证和测试方面。

它缺乏一些高级特性,如面向对象编程、高级验证构造和系统级建模。

SystemVerilog

基本特性:

SystemVerilog是Verilog的扩展,包含了Verilog的所有功能,并增加了许多新的特性。

它引入了面向对象编程(OOP)的概念,如类、继承、封装和多态性,这使得设计和验证更加模块化和可重用。

SystemVerilog提供了高级的数据类型、断言、覆盖率指令和随机化特性,这些特性在验证复杂系统时非常有用。

它支持系统级建模和低级别的硬件描述,使得设计可以从概念验证到硅实现的整个过程都得到支持。

应用范围:

SystemVerilog主要用于复杂的SoC(系统芯片)设计和验证,尤其是在需要高级验证技术和系统级建模的场景中。

它适用于验证复杂的IP核、总线接口、内存控制器以及多处理器系统。

优势:

SystemVerilog的高级特性使得设计和验证过程更加高效,减少了设计周期和成本。

它的面向对象特性和随机化特性使得创建复杂的测试环境和验证平台成为可能。

语法上两者的主要区别:

在语法上,Verilog和SystemVerilog之间存在一些显著的区别。这些区别反映了SystemVerilog在Verilog基础上增加的高级特性和功能。以下是一些主要的语法差异:

- 数据类型和变量声明

Verilog:

变量声明必须指定数据类型(如wire, reg, integer等)。

变量类型必须一致,不能在同一个模块中混用不同类型的变量。

SystemVerilog:

引入了更多的数据类型,如logic, bit, byte, shortint等。

支持类型自动推导,变量可以在声明时省略类型,编译器会根据上下文自动推断。

支持结构体(struct)和联合体(union)等复杂的数据类型。

2. 面向对象编程

Verilog:

不支持面向对象编程。

SystemVerilog:

支持类(class)和对象的概念,允许创建类的实例,支持继承、封装和多态性。

可以使用new操作符创建对象,并使用dot操作符访问对象的成员。

3. 过程块和函数

Verilog:

使用always块来描述时序逻辑和行为模型。

使用task和function来定义过程和函数,但不支持函数作为参数传递。

SystemVerilog:

引入了always块的改进版本,如always_comb, always_ff, always_latch等,以提供更精确的时序控制。

函数(function)可以作为参数传递,支持返回值,并且可以重载。

4. 断言和覆盖率

Verilog:

不原生支持断言和覆盖率。

SystemVerilog:

支持assert语句和covergroup,用于验证设计的正确性和覆盖率。

可以定义属性(property)和假设(sequence),用于形式验证和测试。

5. 随机化和约束

Verilog:

不支持随机化和约束。

SystemVerilog:

提供了随机化(randomize)方法和约束(constraint)系统,用于生成随机测试和创建复杂的测试场景。

支持随机化序列和约束块,使得测试更加自动化和系统化。

6. 并发和同步

Verilog:

并发语句(如assign和always块)和同步语句(如begin和end)的使用较为分离。

SystemVerilog:

支持更高级的并发构造,如fork和join,以及disable语句,用于更精细的控制并发执行和同步。

7. 命名和作用域

Verilog:

命名规则相对简单,作用域主要依赖于模块和端口。

SystemVerilog:

引入了包(package)的概念,允许跨模块共享类型定义和函数。

支持命名空间(namespace),提供了更好的作用域管理。

这些语法上的差异使得SystemVerilog在设计和验证复杂系统时提供了更多的灵活性和功能。随着电子系统设计的不断进步,SystemVerilog的这些高级特性变得越来越重要。

二、流水灯

代码

led_flow.sv

module led_flow (input logic clk, // 时钟信号input logic rst_n, // 复位信号(低有效)output logic [7:0] led // 8位LED输出

);logic [23:0] counter; // 24位计数器,用于产生慢时钟信号// 计数器逻辑always_ff @(posedge clk or negedge rst_n) beginif (!rst_n)counter <= 24'd0;elsecounter <= counter + 1;end// LED流水灯逻辑always_ff @(posedge counter[23] or negedge rst_n) beginif (!rst_n)led <= 8'b0000_0001;elseled <= {led[6:0], led[7]};end

endmoduletestbench

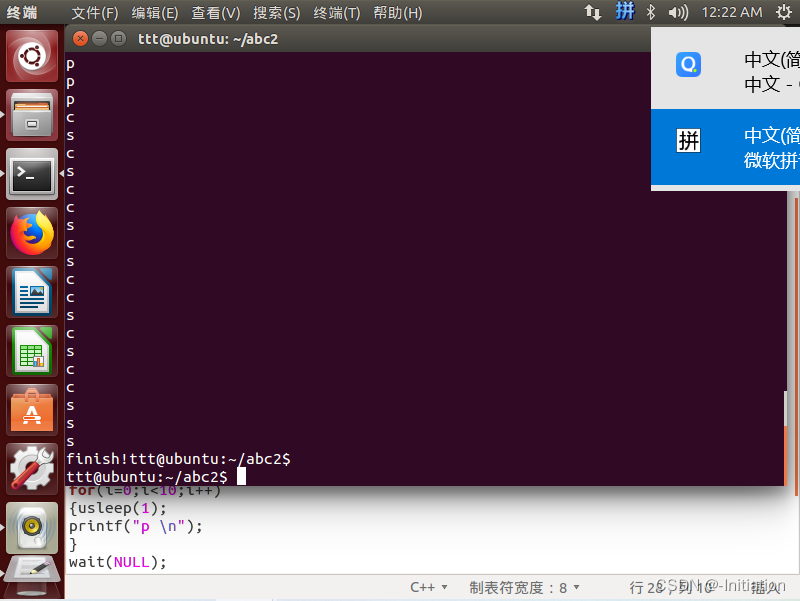

module led_flow_tb;logic clk;logic rst_n;logic [7:0] led;// 实例化待测试的流水灯模块led_flow uut (.clk(clk),.rst_n(rst_n),.led(led));// 时钟信号生成initial beginclk = 0;forever #10 clk = ~clk; // 50MHz时钟周期为20nsend// 测试逻辑initial begin// 初始化信号rst_n = 0;#100;rst_n = 1;// 仿真运行一段时间后结束#1000000;$stop;end

endmodule三、实验效果