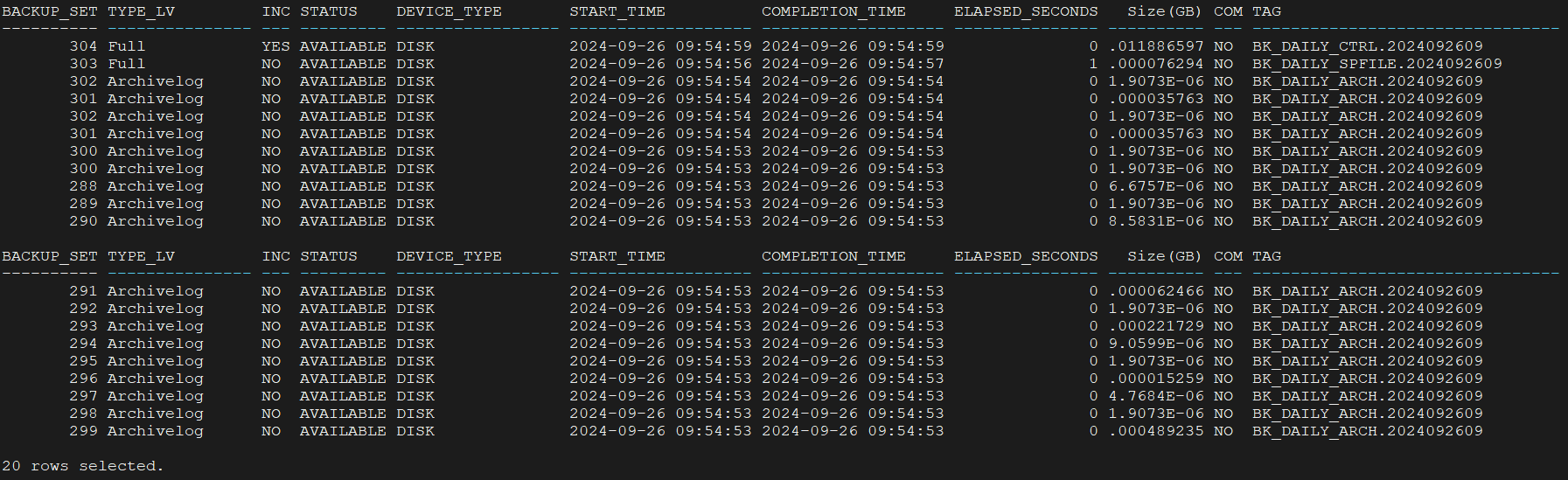

| 内容 | J3 | J5 | J6E |

| CPU | 4核Cortex-A53 1.2GHz | 8核Cortex-A55 1.2GHz | 6核Cortex-A78AE 1.5GHz |

| MCU | / | MStar 双核锁步Cortex-MStar | 2核Cortex-R52+ One DCLS core pairand one Split-Lock core 1.2GHz |

| GPU | / | / | Mail-G78AE 800MHz 100 FP32 GFLOPS |

| BPU | 2*Bernoulli-architecture 5TOPS | 2*Bayes-architecture 128TOPS | 1*Nash-architecture 80TOPS |

| MIPI | 4*2.5G MIPI CSI RX 2*2.5G MIPI CSI TX | 3*4.5G MIPI CSI RX 2*2.5G MIPI CSI TX | |

| I2C | 6 | 8 | 6(CPU) 4(MCU) |

| PCM | 1 | / | 2(CPU) |

| DVP | 1 | 1 | / |

| USB2.0 | 1(CPU) | ||

| SPI | 3 | 4*SPI master 2*SPI slave 其中1路复用 | 2(Master/CPU) 6(4*Master-Slave+2*Master/MCU) |

| UART | 4 | 4 | 4(CPU) 3(MCU) |

| CAN | / | 4 | 10 |

| ETH | 1*1Gb | 2*1Gb 其中一路支持TSN | 2*1Gb(CPU) 其中一路支持TSN 1*1Gb(MCU) 支持TSN |

| PCIe | / | Gen3 2Lane | Gen3 4Lane |

| PWM | / | 2 | 12(MCU) |

| LPWM | / | 16 | √ |

| EMMC | 1 | 1 | 1 |

| SD/SDIO | 1 | 1 | 1 |

| DSP | 1 | 2 | 1 |

| I2S | 2 | 2 | 2 |

| CAN | / | / | 10(MCU) |

| LIN | / | / | 3 |

| DRAM | LPDDR4/LPDDR4X | LPDDR4/4X | LPDDR5/4X |

功能安全入门-地平线J5功能安全岛(FSI)分

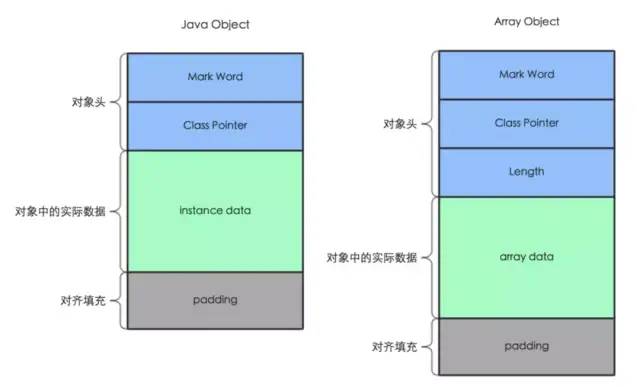

既然大家玩FSI安全岛的概念,那么跟汽车有关系的SoC肯定也要有这东西。例如国内的地平线J5上,如上图所示就有安全岛,明确支持了双核锁步MCU。

更加详细的可以看芯片框图如下:

1. 整体介绍

地平线J5 SoC系列是根据ISO26262开发的,并且具有全面的安全方案,以达到较高的汽车安全完整性水平(ASIL),这对ADAS和自动驾驶应用至关重要。

安全子系统是一个中央错误收集和处理系统。它由双核锁步皮层MStar、FCHM模块和丰富的外设组成,包括以太网、CAN FD、UART、SPI、PVT、CMM、计时器、SPIN_LOCK、WDT、I2C等。

双核锁步Cortex MStar处理器有指令TCM和数据TCM,每个都有双字数据宽度。MStar处理器配置了64KB ITCM、32KB DTCM、16KB ICACHE和16KB DCACHE。S-AHB接口用于对内存映射的SRAM、外围组件和外部设备的指令获取和数据访问。双核锁步DMAC支持4个DMAC通道和16个硬件握手。

FCHM模块提供了一种用于收集错误通知并引导设备进入安全状态的硬件机制。它主要收集三种类型的错误:

- 软件错误:由软件触发写FCHM配置寄存器,最大64错误源,必须是关键错误,可以设置是否重启,有使能位

- 硬件错误:512个硬件错误源,可以设置关键错误和非关键,可以设置是否重启,有使能位

- 外部错误:SoC外部设备错误,32个错误源,都是非关键错误,可以设置A核或者MSTAR处理,软件决定处理策略。

每个硬件错误都可以配置为严重错误或非严重错误。如果断言一个关键错误或自检BIST错误,两个错误pad将以重复或反向模式输出错误,以便系统能够感知到SoC的错误。有关FCHM的更多详细描述,请参考安全手册。SPI/I2C可以与具有安全协议的系统进行通信,这可以在安全手册中找到。

功能安全的设计是应用在SoC的各个模块,FSI只是集中处理错误的一个模块,各个模块根据自己的需求和预算选择合适的ASIL等级设计。特别是一些关键模块,例如J5 A核上的GIC 500就进行了功能安全设计,其他例如ISP、MIPI等关键硬件模块。

2. MStar

MStar处理器是一种高效节能和可配置的处理器,旨在用于需要快速中断响应特性的微控制器和深度嵌入式应用程序。该处理器基于ARMv8-M架构,主要用于安全性很重要的环境中。

两个处理器在系统启动期间初始化为相同的状态,它们接收相同的输入(代码、总线操作和异步事件),因此在正常操作期间,两个处理器的时钟状态是相同的。据说他们是同步运作的。步进技术假设一个错误的处理器会导致不同两个处理器的状态不同,最终将表现为不同的输出,所以步进系统监控两个处理器的输出和标志一个错误的差异。

3. 其他外围器件

3.1 SYSCNT

J5有一个系统计数器(SYSCNT),用于生成64位滚动时间,并将其分发到用于对齐跟踪信息的其他系统组件。采用锁定步骤,以支持功能安全。

SYSCNT有两个APB接口:一个用于读取计数器值和管理寄存器的只读接口,以及一个编程接口。

锁定步骤SYSCNT组件实现了一个可编程定时器,以生成一个64位的滚动时间,用于在不同的系统组件内的时间戳对齐。SYSCNT使用预先配置的计数时钟,特定频率应该是每秒。

3.2 PIN

该设备有大量的数字盘和模拟盘,以满足与其他外部设备的交互,包括电源pads和信号pads。所有的护垫都处于超低功耗域,使来自外部设备的唤醒事件能够唤醒当前的设备,并简化设计。

3.3 GPIO

通用输入/输出(GPIO)外设提供专用的通用引脚,可以配置为输入或输出。当配置为输出时,用户可以写入内部寄存器来控制在输出引脚上驱动的状态。当配置为输入时,用户可以通过读取内部寄存器的状态来获得输入的状态。

3.4 PVTC

PVTC用于控制过程检测器(PD)、VM和TS传感器的多个控制器的行为。CPU通过NoC和APB总线访问PVTC寄存器。PVTC使用串行接口来控制传感器,当传感器相对于PVTC进行远程放置时,串行接口大大减少了需要路由的信号数量。在安全子系统中实例化了两个PVTC,每个都有8个温度传感器(TS)、1个电压监视器(VM)和4个PD。

PVTC有以下关键功能:

- 写锁功能提供保护防止无意重新配置

- 自动轮询电压监测测量通道(通常16小时)

- 最小化信号路由,嵌入式模块串行连接使用星形拓扑

- 时钟合成器生成串行时钟和定时控制的嵌入式模块

- 串行接口包括远程数据回路支持系统集成测试

- 嵌入式模块可以单独禁用(时钟门关闭)

- 数据恢复可能是中断驱动,轮询或纯粹基于警报事件

- 为了支持代码开发,可以为测试目的强制中断

- 在过渡期间为空白恢复的数据提供一个样本丢弃功能。两个可编程(上升或下降)硬件警报包含每个TS和PD设备

- 两个可编程(上升或下降)硬件警报包含每个VM CH

- 状态寄存器记录每个TS,PD和VM CH接收的最小和最大数据值

- 样本计数器提供TS,VM和PD设备提供IRQ通电定时器,以支持TS、PD和VM设备

- 测试访问模式,允许控制器的串行测试访问数据寄存器连接到IJTAG(IEEE-1687)风格的嵌入式测试网络

3.5 UART

通用异步接收器/发射器(UART)是一种符合AMBA3.0标准的高级外围设备总线(APB)从属设备。UART根据行业标准16550进行建模。但是,寄存器地址空间被重新定位到32位数据边界。UART可以使用GUI进行配置、合成和验证。UART用于与:

- 外设

- 调制解调器(数据载体设备,DCE)

- 数据集进行串行通信

3.6 SPINLOCK

旋锁模块最多实现128个旋锁键对,每个旋锁键对由8位Get_key和8位Call_key组合。Get_key和Call_key使用奇偶校验方案来实现功能安全。奇偶校验方案是每8个数据位有1个奇偶校验位。每个旋转锁键对都支持错误注入功能。

旋锁有以下关键功能:

- 符合APB 3.0规范

- 每个Get_key和Call_key结合一个旋锁键对

- Get_key和Call_key有8位物理配置寄存器

- 最大旋锁键对128奇偶校验CSR寄存器,1奇偶校验位每8数据位

- 支持故障注入检查奇偶校验生成器

3.7 Timer

设备中有2个锁步定时器模块,它们都在安全子系统中。所有计时器都包括特定的功能,以产生准确的操作系统中断的提示。

每个计时器都可以从几个不同的独立时钟上进行时钟。时钟源的选择来自于CGM_TIMER0_SEL/CGM_TIMER1_SEL中的寄存器。 锁步计时器有以下功能:

- APB2接口支持-

- 最多8个可编程计时器为1计时器实例

- 32-位计时器计数器宽度支持两种操作模式:自由运行和用户定义的计数支持独立时钟的计时器

- 主动高中断

- 组件生成一个中断结合所有计时器中断

- 实例化2锁步计时器,每个有8个计时器

- 不支持PWM模式

3.8 WDT

J5中有11个Window WDT(WWDT)模块,它们都在SafetySYS中。WWDT能够根据配置产生超时中断/重位。所有的WWDT模块都被映射到不同的核心,每个WWDT都属于一个核心。WWDT可以从几个不同的独立时钟上进行时钟。时钟源可以从CGM_WDT_SEL中的寄存器中选择。

3.9 VIC

VIC是位于Acore、Mcore和两个vdsp之间的虚拟中断。一个核心可以通过配置几个寄存器来向另一个核心发送一个虚拟中断。

VIC具有以下关键功能:

- A55向A55 MStar发送虚拟中断、VDSP0和VDSP1

- MStar向A55、MStar、VDSP0和VDSP1

- VDSP0向A55、MStar、VDSP0和VDSP1

- VDSP1向A55、MStar、VDSP0和VDSP1发送虚拟中断

4. J5安全机制

4.1 错误管理

按错误检测的时机,错误分为两类:

- 系统启动阶段:Logic BIST、Memory BIST、Self-Test。

- 系统运行阶段:软件STL或者硬件IP内集成的方法

对于错误需要定级别,并且需要考虑故障的处理策略方法、反应时间、监测时间等

4.2 安全监测

J5 SoC有53个功能IP常用的检查机制,对IP进行功能失效分析及影响评估,进而进行处理。常用的功能安全监测和处理方法如下:

- 寄存器parity校验

- 存储的CRC校验

- 存储的ECC校验

- 功能IP的锁步

- APB总线超时检测

- 设备内存和寄存器写后读回检查

- 中断触发后读寄存器确认

- 接口读检测

- IP硬件自检

- watchdog超时检查

- CPU STL

后记:

功能安全有很多策略,内功心法ISO26262中也没明确说我们要用什么技术去实现,主要还是需要根据自己的业务或者重要功能去做功能安全比较好。例如智能驾驶SoC中主要保证摄像头雷达的数据处理,整个数据处理链条上的软硬件就必须都要加强功能安全设计,这样自动驾驶的时候才能保证人的生命安全。

功能安全放在硬件上的成本是比较贵的,但是比软件可靠,放软件也会降低执行效率,所以不是什么东西都需要功能安全,根据我们的业务需求去权衡