开篇

你是否曾对 CPU 的工作原理充满好奇,以及简单的晶体管又是如何组成逻辑门,进而构建出复杂的逻辑电路实现?本文将以知名的 6502 CPU 的电路图为例,介绍如何阅读 CPU 电路图,并向你演示如何从晶体管电路还原出逻辑门电路。通过这篇文章的引导,你将能够揭开 CPU 复杂设计的面纱,一窥其内部运作的奥秘。

示例图

首先,让我们先大致了解一下 6502 CPU 的晶体管电路图。目前我能找到的电路图有两个。一个是一份 PDF 文档(6502 Schematic.pdf),这份文档中的电路图虽然没有详细到每根线都画出来,但关键组件的电路图都有,算是很简洁的一份电路图。另一份是电路图是 GitHub 上有人整理的一个 SVG 版本的电路图(下图),这份电路图非常详尽,详细到每根线、每个晶体管都有,是非常好的资源。

MOSFET

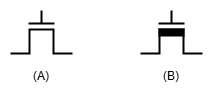

仔细研究上面的电路图,可以发现图中一共可总结出两种元件,如下图:

它们都是一种 MOSFET(金属氧化物半导体场效应晶体管),再具体点,它们都是一种 N 型 MOSFET,简称 NMOS。

MOSFET 可以看作一种由电压控制的特制开关,其中 NMOS 在控制电压为高电平(逻辑 1)时导通,低电平(逻辑 0)时断开。

上图中,上部中间的连接端就是控制端。

耗尽型 NMOS

既然都是 NMOS,那 A 和 B 的区别是什么呢?答案是,A 属于增加型 NMOS,而 B 属于耗尽型。

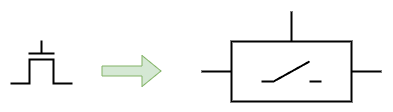

耗尽型 NMOS 的作用是充当负载,为其它 MOS 提供电压电流,相当于一个电阻。充当负载时,它的一个连接端与供电相接(如下图),另一个连接端与控制端连接在一起,使它处于常导通状态。

上图中,小圆圈表示供电。

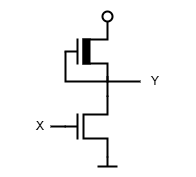

非门

根据 NMOS 高电平导通的特性,将它的一个端接地,另一个连接端搭配一个耗尽型 NMOS 的负载就可以构成一个非门。

当 X 为高电平时,下面的 NMOS 导通,Y 相当于直接接地,此时 Y 为低电平;当 X 为低电平时,下面的 NMOS 截止,Y 相当与供电连接,此时 Y 为高电平。综上,这个电路是一个非门逻辑电路。

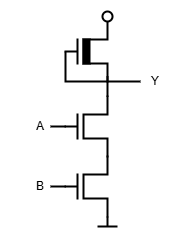

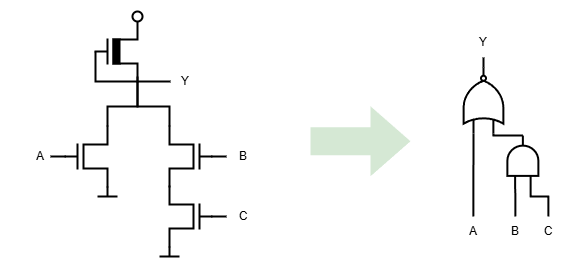

与非门

在非门的下方再串联一个 NMOS,就得到了与非门。

或非门

在非门的旁边再并联一个 NMOS,就得到了或非门。

锁存器

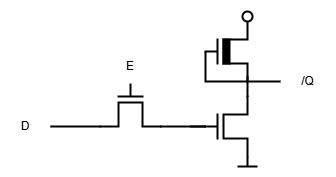

电路图中还有一类非常常见的结构,如下图:

这种结构大概率表达的是一种锁存器 – D-锁存器。锁存器是一种基本的存储元件,相当于一个 1 比特的内存,在时序逻辑中用于存储和保持状态信息。锁存器的使能端(E 端)常与时钟信号连接,因此若在电路图中看到时钟信号接入了使能端,则这样结构很可能是锁存器。初看之下,这样的结构似乎没有道理,为什么一个开关加上一个非门就能存储数据了?其实这里面涉及一些电学知识,这里就不过多阐述了,我们是为了理解电路图,只需记住这样的结构就行了。

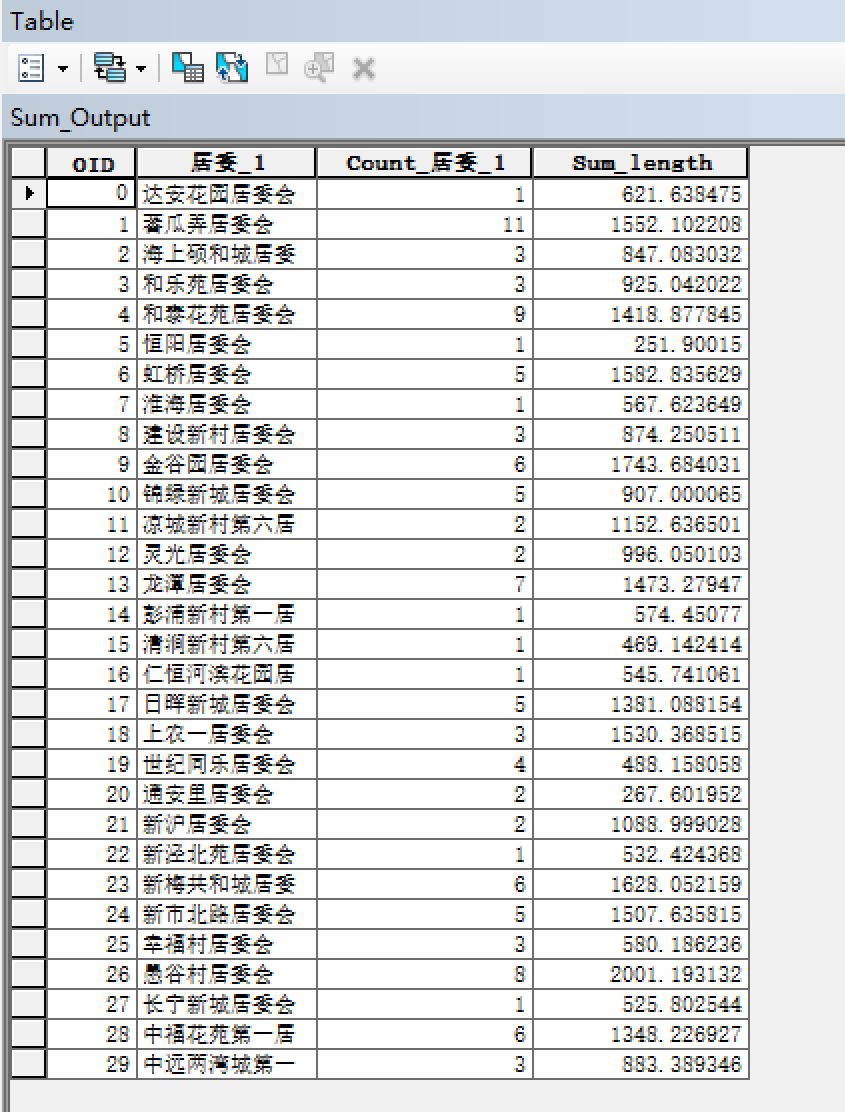

示例

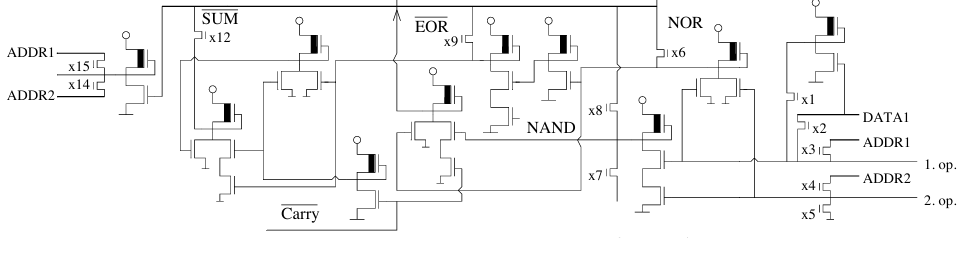

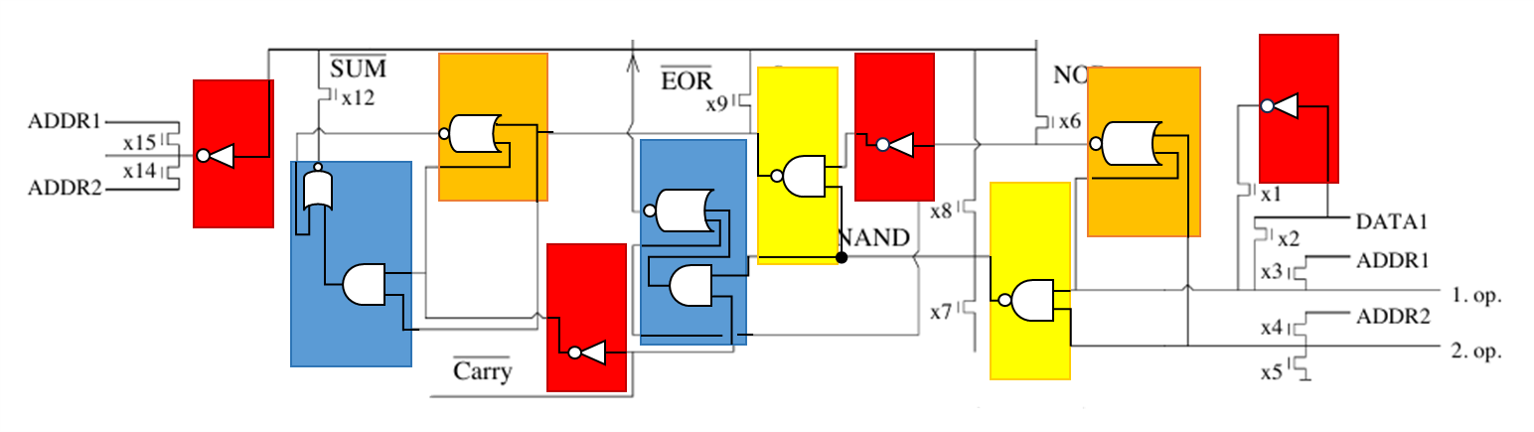

有了上面的基本知识后,我们可以尝试解读一下 CPU 电路图了,看看能不能还原其中的逻辑。以下是 6502 ALU 一个计算单元的电路图(来自 6502 Schematic.pdf),ALU 由 8 个类似的单元串联组成,可完成 8 位二进制数(一个字节)的计算。

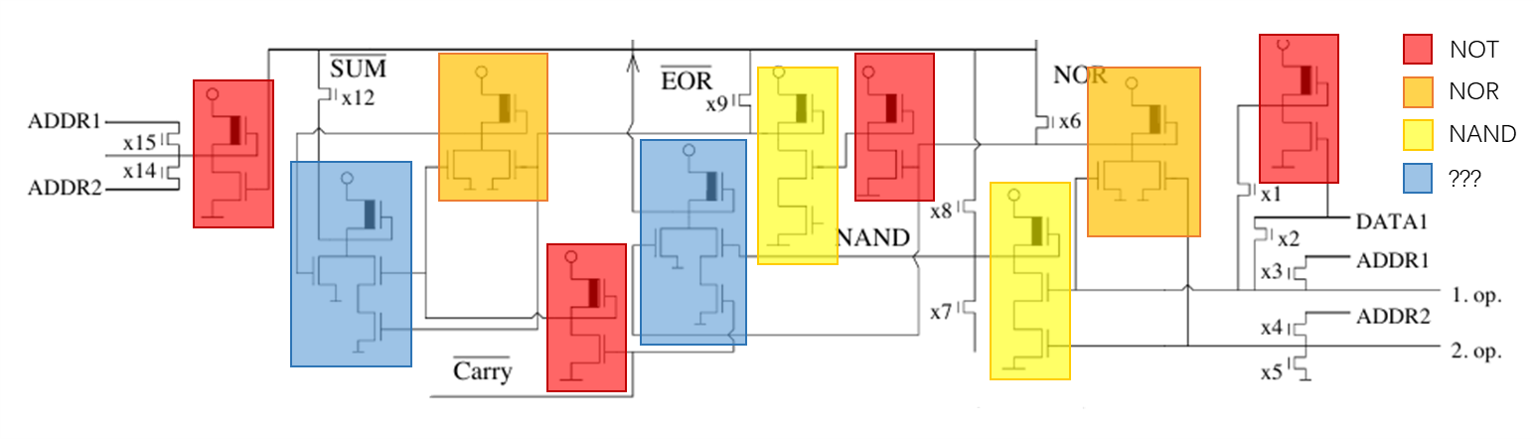

根据上面的知识,可以把相应的逻辑门标注出来:

其中只有蓝色框标记的部分不是基础逻辑门,但是应用非门的分析方法,不难得出它是一个与门和或非门的组合:

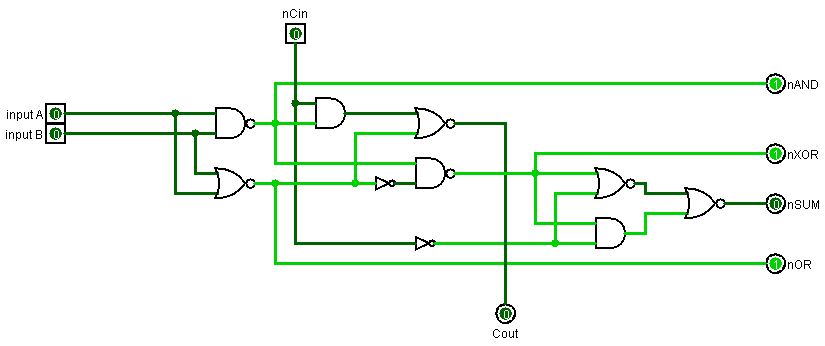

弄清楚之后,再把方块标记的部分转化成逻辑门表示:

未转化成逻辑门的 NMOS 相当于开关,负责数据通路的选择。其中 x1 ~ x5 是输入选择,x6 ~ x12 负责运算选择,x14 ~ x15 负责输出目的地选择。去除掉这些选择器后,这个 ALU 计算单元的纯逻辑门电路如下:

可以看出,这个单元包含一个全加器,并同时可以进行 “与”、“或”、“异或” 运算。

总结

文本介绍了 NMOS 及提示了逻辑门是如何使用 NMOS 构建的,并用一个实际的例子演示了如何从 NMOS 电路图还原逻辑电路。希望本文可以满足你的好奇心,如果大家对 6502 其它部分的原理也感兴趣,欢迎阅读我的后续文章。

参考

- balazs schematic

- 6502 svg schematic

- 【硬核科普】带你认识CPU第00期——什么是MOSFET