1 验证的本质:尽可能的找出设计的bug;

2 测试向量文件

测试文件(testbench)以模拟的方式来验证逻辑时序的正确性,以源的方式来激励用户编写的逻辑功能模块;

3 验证的3要素

(1)灌激励:输入信号

(2)集响应:输出信号

(3)作比较:比较

4 验证平台的发展

Verilog -> C/C++ -> System C -> System Verilog( 有高级语音的兼容性,时序的兼容)

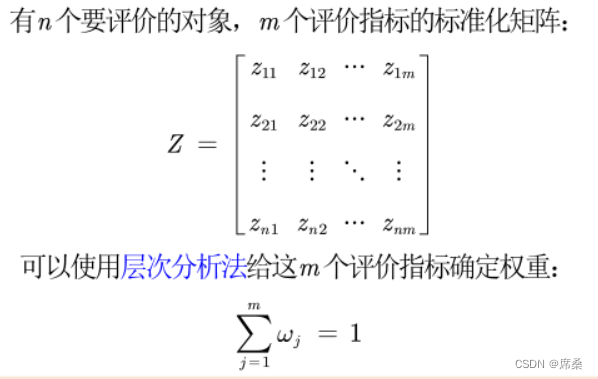

5 验证方法学(UVM)

(1)制定了一种标准的规范

(2)提供底层库

这些方法 :

1:通用 -> 可重用性

2:高效 -> 随机性 解决 :Regression (回归) 、 coverage(覆盖率)

6 验证平台的发展

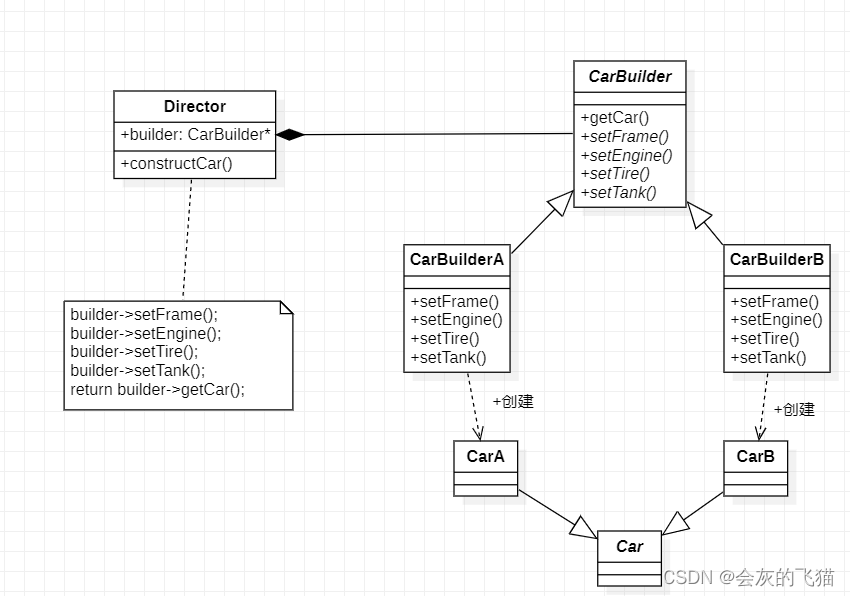

7 简单的UVM平台

8 完整UVM的验证平台

1 DUT 和UVM直接的通信需要interface;

2 UVM的各个Component(组件) 之间采用基于TLM的发送通过数据包的方式通信;

3 Sequence和sequencer 启动方式包括:自启动和手动启动;

9 UVM树

10 UVM运行的机制

Phase机制:(阶段)

1.模块直接是并行的

2.模块内是串行的的