专栏前言

本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网

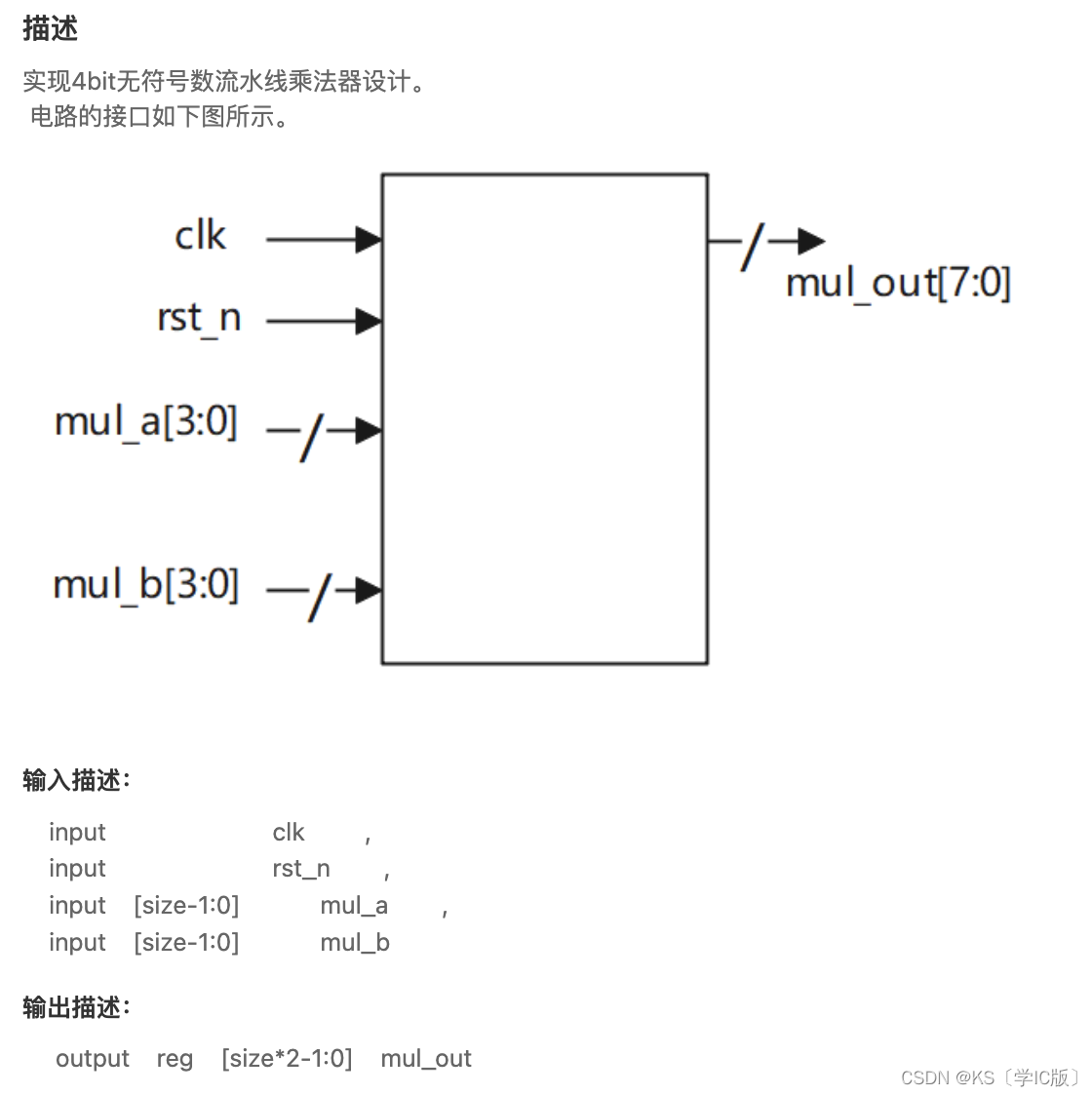

`timescale 1ns/1nsmodule multi_pipe#(parameter size = 4

)(input clk , input rst_n ,input [size-1:0] mul_a ,input [size-1:0] mul_b ,output reg [size*2-1:0] mul_out

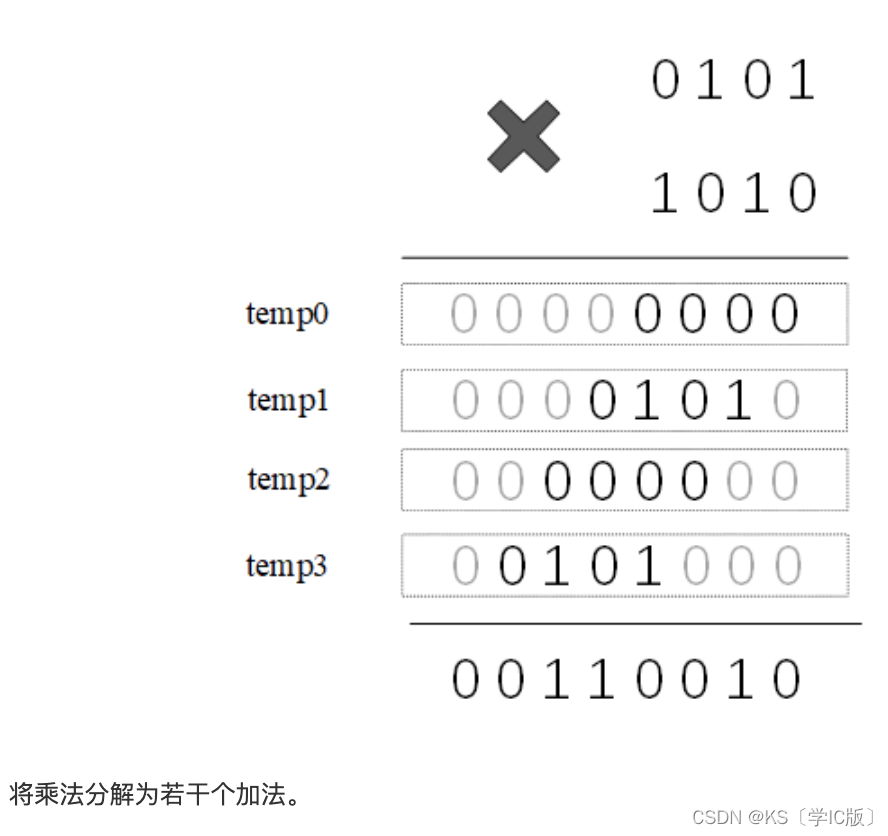

);reg [7:0] sum01, sum23 ;wire [7:0] t0, t1, t2, t3 ; assign t0 = mul_b[0] ? {4'b0, mul_a} : 0 ; assign t1 = mul_b[1] ? {3'b0, mul_a, 1'b0} : 0 ; assign t2 = mul_b[2] ? {2'b0, mul_a, 2'b0} : 0 ; assign t3 = mul_b[3] ? {1'b0, mul_a, 3'b0} : 0 ; always @ (posedge clk or negedge rst_n) begin if (~rst_n) begin sum01 <= 0 ; sum23 <= 0 ; mul_out <= 0 ;endelse begin sum01 <= t0 + t1 ; sum23 <= t2 + t3 ; mul_out <= sum01 + sum23 ;endendendmodule