RV32A\CSR\Counters指令集

- 一、RV32A指令集

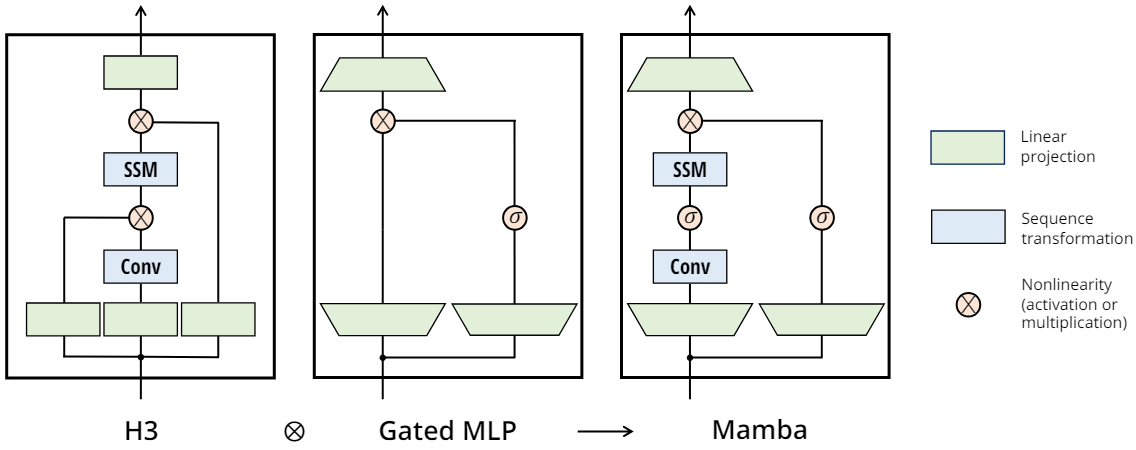

- 1、Load-Reserved/Store-Conditional Instructions

- LR.W

- SC.W

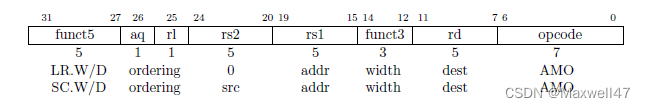

- 2、Atomic Memory Operations

- AMOSWAP.W

- AMOADD.W

- AMOAND.W

- AMOXOR.W

- AMOOR.W

- 二、CSR(Control and Status Register) 指令集

- CSRRW

- CSRRS

- CSRRC

- CSRRWI

- CSRRSI

- CSRRCI

- 三、"Zicntr" and "Zihpm" Extensions for Counters

- 1、 "Zicntr" Extension for Base Counters and Timers

- RDCYCLE

- RDTIME

- RDINSTRET

一、RV32A指令集

“A”的标准原子指令扩展包含以原子方式读取-修改-写入内存的指令,以支持在同一内存空间中运行的多个 RISC-V harts之间的同步。提供的两种形式的原子指令是加载保留/存储条件指令和原子取操作内存指令。两种类型的原子指令都支持各种内存一致性排序,包括无序、获取、释放和顺序一致的语义。这些指令允许RISC-V 支持 RCsc 内存一致性模型。

1、Load-Reserved/Store-Conditional Instructions

aq位代表原子内存操作被视为获取访问

rl位代表原子内存操作被视为释放访问

LR.W

LR.W 指令用于实现“加载-保留”操作,将一个字(32 位)从内存中加载到目标寄存器中,并在加载完成后锁定该内存地址,以确保其他处理器在此期间无法访问该内存地址。其语法如下:

lr.w rd, (rs1)

其中 rd 表示目标寄存器,rs1 表示源寄存器,括号中的内容表示内存地址。

SC.W

SC.W 指令用于实现“存储-条件执行”操作,将一个字(32 位)存储到内存中,并检查此前是否已经执行过 LR.W 操作锁定了该内存地址。如果已经被锁定,则存储失败,否则存储成功。其语法如下:

sc.w rd, rs2, (rs1)

其中 rd 表示目标寄存器,rs1 表示源寄存器1(存储地址),rs2 表示源寄存器2(存储值)。

2、Atomic Memory Operations

原子内存操作 (AMO) 指令为多处理器执行读-修改-写操作同步,并用 R 型指令格式编码。这些 AMO指令从 rs1 中的地址原子加载数据值,将值放入寄存器 rd,将二元运算符应用于加载的值和 rs2 中的原始值,然后将结果存储回去到 rs1 中的地址。

AMOSWAP.W

AMOSWAP.W 指令用于实现“原子交换”操作,其语法如下:

amoswap.w rd, rs2,(rs1)