目录

1.一个八位D/A转换器最小电压增量为0.01V,当输10011100时,输出电压为(D)V

2.下述概念中不属于面向对象这种编程范畴的是(D)

3.组合逻辑电路通常由(B)组合而成

4.三极管作为开关时工作在什么区域(D)

5.在C语言中(以16位PC机为例),5种基本数据类型的存储空间长度的排列顺序为(B)

6.下面表达式计算结果为4的是(D)

7.关于this指针使用做法正确的是(A)

8.在timescale 1ns/10ps的条件下,仿真器在6125ps时的打印时间格式为(C)

9.下列描述中采用时钟正沿触发且reset异步下降沿复位的代码描述是(C)

10.一个数组元素a[l]与下面哪个表示等价(C)

11.在systemverilog中声明随机变量的关键词为(B)

12.在设计中出现端口和驱动该端口位宽不匹配的情况,verilog/systemverilog默认处理方法错误的是(C)

13. linux下,删除文件命令是(C)

14.

15.构成C语言程序的基本单位是(A)

16. 在veriliog HDL的always块语句中的语句是如何执行的(A)

17.在C语言中,一个int型数据在内存中占2个字节,则unsigned int型数据的取值范围为(C)

18.以下哪些是第三代移动通信标准(B)

19.循环体至少被执行次的语句是(C)

20. Verilog HDL中信号没有定义数据类型时,缺省为什么数据类型(B)

21.下面哪个选项不可以消除hold time violation(BCD)

22.下面那些是基于Systemverilog的验证方法学?(ABC)

23.下面哪种方式可以对时序进行检查(BCD)

24.芯片中设计中功耗密度过大,会产生什么不良影响(ABD)

25. 数字电路的验证维度有哪些(ABCD)

26.在验证中下列关于代码覆盖描述错误的是(CD)

27.关于systemerilog中new操作的下列描述中,错误的是(CD)

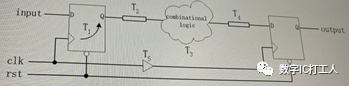

28.以下同步逻辑电路和异步逻辑描述正确的是(BD)

29.超大规模集成电路计中,为了高速设计,采取以下哪些措施(AB)

30.竞争冒险现象可以怎样消除?(ABD)

31.下列关于Setup/Hold Time说法正确的是?(AD)

32.下列数据类型中属于四状态类型的有哪些(ABD)

33.低功耗电路实现的方法有(AC)

34.请找出以下总线中的串行总线(CD)

35.下列哪些方式可以减少亚稳态问题的影响(BD)

36.请判断如下说法是否正确,并针对错误描述具体原因?

37.在一个CPU系统中,有2个Mster通过个2x1的AXI总线访问一个Slave,简述如何构造验证场景来进行验证,并保证验证的完备性

38(1).请列出SRAM与DRAM的不同之处?

(2).请列出一般系统中的Memory hierarchy.并解释系统中为何需要将存储器分层

1.一个八位D/A转换器最小电压增量为0.01V,当输10011100时,输出电压为(D)V

A 1.28

B 1.45

C 1.54

D 1.56

8'b10011100=156

2.下述概念中不属于面向对象这种编程范畴的是(D)

A对象、消息

B继承、多态

C类、封装

D过程调用

过程调用属于面向过程

3.组合逻辑电路通常由(B)组合而成

A记忆元件

B门电路

C计数器

D以上都正确

4.三极管作为开关时工作在什么区域(D)

A饱和区+放大区

B击穿区+截止区

C放大区+击穿区

D饱和区+截止区

5.在C语言中(以16位PC机为例),5种基本数据类型的存储空间长度的排列顺序为(B)

A char<int<long int<=float<double

B char=int<long int<=float<double

C char<int<long int=float=double

D char=int=long int<=float<double

6.下面表达式计算结果为4的是(D)

A 11/3

B 11.0/3

C (float)11/3

D (int)(11.0/3+0.5)

7.关于this指针使用做法正确的是(A)

A 保证每个对象拥有自己的数据成员,但共享处理这些数据的代码

B 保证基类私有成员在子类中可以被访问

C 保证基类保护成员在子类中可以被访问

D 保证基类公有成员在子类中可以被访问

8.在timescale 1ns/10ps的条件下,仿真器在6125ps时的打印时间格式为(C)

A 6

B 61

C 613

D 6125

9.下列描述中采用时钟正沿触发且reset异步下降沿复位的代码描述是(C)

A always@(posedge clk or negedge reset) if(reset)

B always@(posedge clk or reset) if(reset)

C always@(posedge clk or negedge reset) if(!reset)

D always@(negedge clk or posedge reset) if(reset)

10.一个数组元素a[l]与下面哪个表示等价(C)

A *a+1

B a+1

C *(a+1)

D &a+1

11.在systemverilog中声明随机变量的关键词为(B)

A randa

B randc

C randomize

D urandom_range

rand和randc

12.在设计中出现端口和驱动该端口位宽不匹配的情况,verilog/systemverilog默认处理方法错误的是(C)

A如果端口的位宽和驱动该端口的信号位宽相同,则该值可以无变化的通过该端口

B如果驱动端口比端口的接收端的位宽多,则驱动信号的高位bit会被截断

C如果驱动端口比端口的接收端的位宽多,则驱动信号的低位bit会被载断

D如果驱动端口比端口的接收端的位宽少,则依据verilog的赋值规则进行高比特位扩展

13. linux下,删除文件命令是(C)

A mkdir

B rm

C mv

D del

mkdri 创建目录

rm 删除

mv 改名或移动

del

14.

timescale 1ns/1ps

fork

begin #1;end

begin #2;end

join_none

$display($time);

上述代码中需要等待多长时间?(C)

A 1ns

B 2ns

C 0ns

D 3ns

fork_join none不会等待子线程结束

15.构成C语言程序的基本单位是(A)

A 函数

B 过程

C子程序

D 子例程

16. 在veriliog HDL的always块语句中的语句是如何执行的(A)

A 顺序

B 并行

C 顺序或并行

D 不一定

17.在C语言中,一个int型数据在内存中占2个字节,则unsigned int型数据的取值范围为(C)

A 0~255

B 0~32767

C 0~65535

D 0~2147483647

18.以下哪些是第三代移动通信标准(B)

A EDGE

B TD-SCDMA

C LTE

D WIFI

第三代移动通信系统主要标准有WCDMA、CDMA2000、TD-SCDMA

19.循环体至少被执行次的语句是(C)

A for循环

B while循环

C do循环

D 任何一种循环

for(i=0; i<3; i++) { console.log('do')}; 若开始满足 i>=3 ,则不执行

while(i) ... ; 若 i 开始为假,则不执行

do xxxxx while(i); 字面理解,先do再while,不管是否满足i,都会do一次,即最少执行一次

20. Verilog HDL中信号没有定义数据类型时,缺省为什么数据类型(B)

A reg

B wire

C tri

D z

21.下面哪个选项不可以消除hold time violation(BCD)

A 插入buff

B 提高时钟频率

C 降低时钟频率

D 提高电压

hold time 与时钟频率没有关系,前两套也出现过。

22.下面那些是基于Systemverilog的验证方法学?(ABC)

A VMM

B OVM

C UVM

D AVM

23.下面哪种方式可以对时序进行检查(BCD)

A 即时断言

B 并发断言

C 建立时间约束

D 保护时间约束

24.芯片中设计中功耗密度过大,会产生什么不良影响(ABD)

A Hot-spot

B电压下降

C不满足时序约束

D封装成本变高

hot-spot,即芯片上功耗和电源噪声最大的地方

封装成本变高--功耗密度过大显著问题就是需要考虑散热

功耗密度过大必然要降频,提高频率可能会导致不满足时序约束,降频应该不会(个人看法)

25. 数字电路的验证维度有哪些(ABCD)

A完备性

B复用性

C高效性

D满足性能

26.在验证中下列关于代码覆盖描述错误的是(CD)

A代码覆盖率包括语句覆盖率

B代码覆盖率包括条件覆盖率

C代码覆盖率包括功能

D代码覆盖率达到100%说明所有Bug已清除

27.关于systemerilog中new操作的下列描述中,错误的是(CD)

A 它可以用来动态创建对象和对象数据

B使用它创建对象时调用构造函数

C new操作被定义成一个需要有返回类型的函数

D使用它创建对象数组时必须指定对象的初始值

28.以下同步逻辑电路和异步逻辑描述正确的是(BD)

A同步逻辑电路是时钟之间没有固定的因果关系,异步逻辑电路是各时钟之间有固定的因果关系

B同步逻辑是由时序电路(寄存器和各种触发器)和组合逻辑电路构成的电路,其所有的操作都是在严格的时钟控制下完成的。

C异步逻辑电路不同时钟域之间不需要进行时钟同步

D 异步逻辑可能存在多个时钟信号,或者不存在时钟信号,电路中一个逻辑的变化就会引起整个电路逻辑的变化。

29.超大规模集成电路计中,为了高速设计,采取以下哪些措施(AB)

A 流水线设计

B 并行化设计

C 资源共享

D 串行化设计

30.竞争冒险现象可以怎样消除?(ABD)

A 加入滤波电容

B引入同步机制

C不加选通信号

D增加冗余逻辑

在有竞争冒险存在的情况下,而负载又是对脉冲敏感的电路,那么就应设法消除。消除竞争冒险常用方法有:增加冗余项、接入滤波电容和引入封锁脉冲或选通脉冲等。

IC笔试:2022紫光展锐数字芯片提前批笔试_acmgotoac的博客-CSDN博客

31.下列关于Setup/Hold Time说法正确的是?(AD)

A如果DFF的Hold时间不满足,通常可以通过增加数据路径延时来解决

B如果DFF的Setup时间不满足,通常可以通过增加数据路径延时来解决

C如果DFF的Hold时间不满足,通常可以通过增加时钟路径延时来解决

D如果DFF的Setup时间不满足,通常可以通过增加时钟路径延时来解决

32.下列数据类型中属于四状态类型的有哪些(ABD)

A int

B logic

C bit

D time

33.低功耗电路实现的方法有(AC)

A 降低工作电压

B增加负载电容

C降低电路面积

D尽可能提高电路性能

34.请找出以下总线中的串行总线(CD)

A AXI

B SDIO

C UART

D IIC

35.下列哪些方式可以减少亚稳态问题的影响(BD)

A 提升系统时钟频率

B 用反应更快的FF

C 架构上增加data toggle rate

D 改善时钟质量

应该减小数据翻转率,最终目的降低频率。

36.请判断如下说法是否正确,并针对错误描述具体原因?

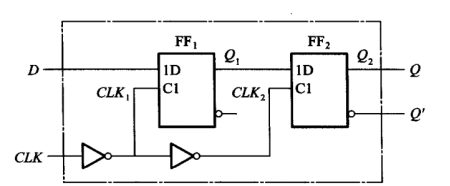

1.可以通过两级触发器防止亚稳态传播,也可以用来同步多bit信号; X

同步多bit的前提是多bit信号是顺序变化且闭合的格雷码

2.时钟域A的多bit信号一定要经过同步才能被时钟域B采用; X(存疑)

多bit信号稳定时不需要同步,直接采

IC笔试:2022紫光展锐数字芯片提前批笔试_acmgotoac的博客-CSDN博客

3.如果DFF的hold时间不满足,可以通过降低时钟频率来解决; X

hold和时钟频率无关

4.假定没有毛刺产生,异步复位信号可以不管时钟,只要复位信号满足条件,就能完成复位动作; 正确(存疑)

2022紫光展锐数字芯片提前批笔试_狗哥天下第一的博客-CSDN博客

37.在一个CPU系统中,有2个Mster通过个2x1的AXI总线访问一个Slave,简述如何构造验证场景来进行验证,并保证验证的完备性

38(1).请列出SRAM与DRAM的不同之处?

存储方式不同

DRAM一位数据存储在一个电容器中,根据电容的电荷量判断状态,SRAM一位数据需要六个MOS管

主要用途不同

SRAM因为其速度比较块一般用作Cache,而DRAM因为相对比较便宜,所以比较适合作为主存

是否需要刷新电路

由于DRAM数据存储在电容器中,在读取数据时会导致蒂安和流失,因此需要额外加一个刷新电路,而SRAM不需要刷新电路

价格不同

由于DRAM制作比较简单,因此其价格相对便宜,而SRAM价格相对比较高

功耗不同

由于DRAM需要在运行时不断地刷新存储,因此功耗更大,SRAM不需要刷新,因此功耗较小

速度不同

DRAM速度比SRAM速度慢

(2).请列出一般系统中的Memory hierarchy.并解释系统中为何需要将存储器分层

下图是一个典型的存储器层次结构图,一般而言,从高层往底层走,存储设备变得越来越慢,越来越便宜,越来越大。

寄存器-(通过指令)-Cache-(通过块)-内存-(通过页表)-磁盘-(通过文件)-磁带