单选题

1、以下关于 System Verilog 的描述,正确的是( )

A. sv 中可以用 logic 代替 Verilog 中的 wire 和 reg 类型

B. sv 中, 定义成 reg 的信号会被综合成触发器

C. sv 中的 function 语言不可被综合

D. 其他都不正确

E. sv 是提供给验证使用的, 因此其不能被综合

答案:

解析:2、UVM 层次化结构中,最顶层的部件类型是?( )

A. uvm_test

B. uvm_root

C. uvm_root

D. uvm_component

答案:

解析:3、数字信号上采样时,一般需要添加什么样的滤波器,完成功能为?( )

A. 高通,抗混叠滤波

B. 低通,抗周期延拓

C. 低通,抗混叠滤波

D. 高通,抗周期延拓

正确答案:B

新芯设计:

这是属于信号处理部分的知识,虽然是基础知识但是还是需要一定的功底的

首先信号的采样分为上采样和下采样,从时域上看,上采样是按一定的比例增加点数,下采样是按一定的比例减少点数;从频域上看,上采样导致了频谱延拓,下采样导致了频偏混叠,二者都会导致频偏的远端受到一定的影响,因此需要低通滤波器来消除频谱远端造成的影响4、下列不属于异步总线的是?( )

A. SPI

B. USB

C. UART

D. IIC

答案:

解析:5、电路的逻辑功能特点是, 任意时刻的输出仅仅取决于该时刻的输入, 与电路原来的状

态无关( )

A. 静态逻辑

B. 组合逻辑

C. 动态逻辑

D. 时序逻辑

正确答案:B

新芯设计:基本知识

A:静态逻辑,以 SRAM 为例

C:以 DDR 为例

D:以 Register 为例6、在芯片设计流程当中, 通常会进行后仿真(Post-Simulation) ,关于后仿的作用, 以下说法不正确的是( )

A. 抽检 Netlist 是否和 RTL 功能一致

B. 抽检电路中是否出现有害的 Glitch

C. 抽检时序是否有违规

D. 抽检电路中是否存在亚稳态

正确答案:D

新芯设计:后仿真和前仿真的主要区别在于是否加入了真实的时序、加入了器件延迟、加入了竞争冒险等等

A、B、C:没错,检查引入真实的时序之后电路功能是否依旧能够正常工作

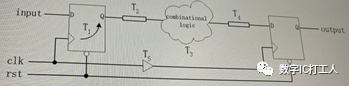

D:电路中的亚稳态是必然存在的7、以下关于异步处理正确的是( )

A. 信号经过两级触发器即可完成异步信号的传递

B. 只要信号传递的两端时钟频率不相等, 即认为是异步信号

C. 异步复位信号需要经过同步处理后再使用是安全的

D. 异步 FIFO 中使用格雷码传递异步计数器可以保证每一拍传递的数据都是准确的

正确答案:C

新芯设计:异步信号的处理也是至关重要的,在芯片设计中不可避免,在芯片量产中也是较大的风险点

A:单比特信号才可以打两拍,此外,打两拍是需要用目的时钟来打

B:异步信号,相位频率都需要不一致才算是异步信号,二者缺一不可

C:异步复位同步释放的处理方式

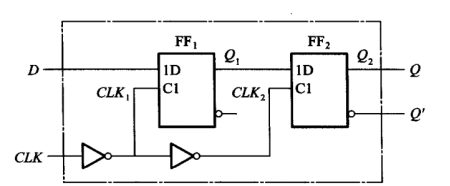

D:异步处理只是减小亚稳态的影响,而不是避免,还是有可能出现较小概率性的数据错误的8、关于跨时钟域电路的设计,以下说法正确的是( )

A. 单比特信号经两级 D 触发器同步后即可进行跨时钟域传递

B. 采用单一时钟的电路不会产生亚稳态

C. 异步 FIFO 的两个时钟频率相同也可以正常工作

D. 跨时钟域电路当中的亚稳态无法消除

正确答案:C

新芯设计:

A:写的太简单了,没有写经过什么时钟域的 D 触发器

B:建立时间保持时间不满足的话,也会产生亚稳态

C:异步 FIFO 的两个时钟一样的话,就当成同步 FIFO 来使用了,是可以正常工作的

D:亚稳态无法消除,这是其特性9、衡量数字通信系统传输质量的指标是( )

A. 信噪比

B. 噪声功率

C. 语音清晰度

D. 误码率

正确答案:D

新芯设计:这是通信系统的概念

A、B、C:信噪比是属于外界的物理指标10、以下代码片段实现的电路功能是( )

input [3:0] in;output [3:0] out;wire [3:0] a,b;assign a=in<<1;assign b=in>>3;assign out=a|b;A. 对输入信号 in 先右移 3 位, 再左移 1 位

B. 对输入信号 in 循环左移 1 位

C. 对输入信号 in 循环右移 3 位

D. 对输入信号 in 先左移 1 位,再右移 3 位

正确答案:B

新芯设计:考验 Verilog 代码结合电路的能力

out = {in[2], in[1], in[0], 1'b0} | {3'b0, in[3]} = {in[2], in[1], in[0], in[3]}

很明显,这是循环左移 1 位,如果要说成循环右移 3 位也是没问题的填空题

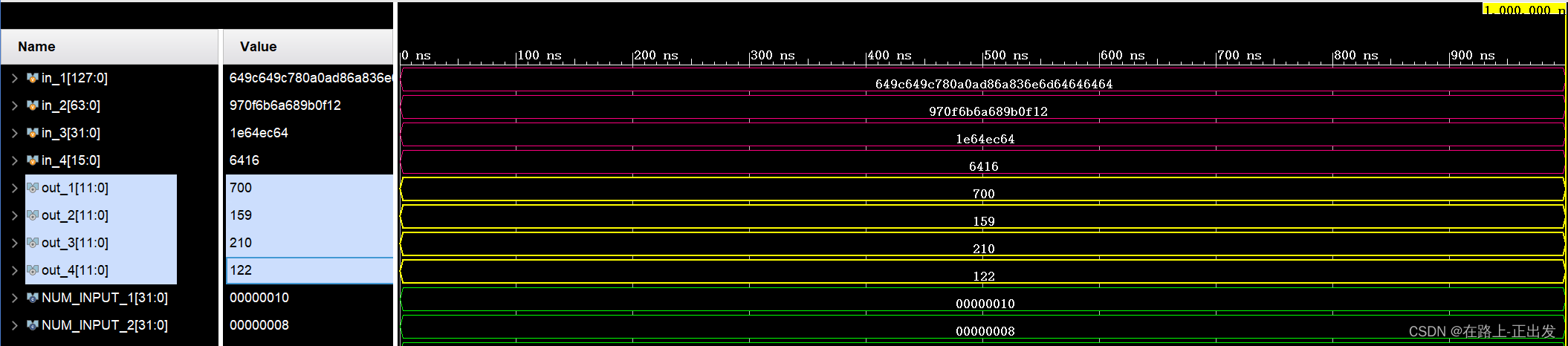

1、Verilog 当中 a=4’b10x1;b=4’b10x1;那么逻辑表达式 a==b 为_______ a===b 为________

2、4bit 的信号输入和 8bit 的信号输入的乘法器内部计算输出信号至少需要______ bit 的位宽

3、通常情况下, 芯片工作温度较________, 工作电压较_______ , 速度最快。

4、以下代码的打印输出是___________

always@(posedge clk)

begin

a=0;

a<=1;

$display(“%0b”,a);

end

5、全部使用组合逻辑实现 A, B, C 的运算实现|A*(B+C)|^2 共需使用_______ 个乘法器与_______个加法器

答案:

解析:问答题

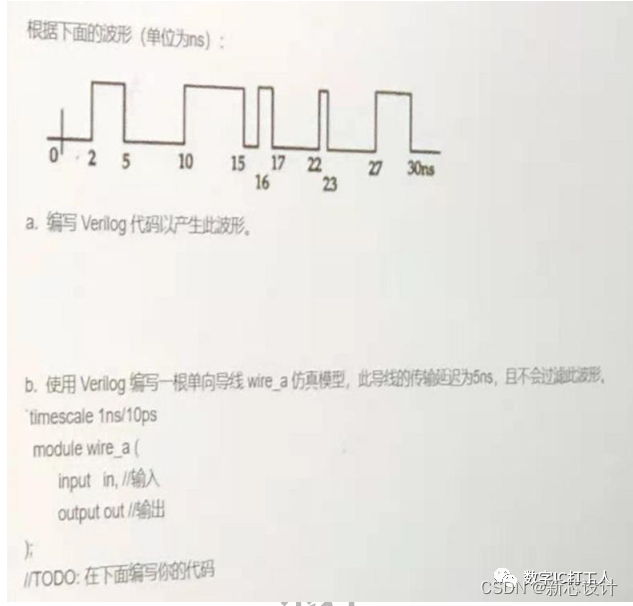

1、

Endmodule

答案:

解析:2、使用 v/sv 编写如下功能模块,求输入信号序列 din 在 din_vld 为高电平的时间段内的次小值与次小值出现的次数

接口信号如下

module sec_min(

input clk,//时钟

input rst_n,//复位

input [9:0] din, //10bit 无符号数

input din_vld, //输入数据有效信号

output [9:0] dout, //次小值

ouput [8:0] cnt //次小值出现的次数。溢出时重新计数

答案:

解析: