1. 场景

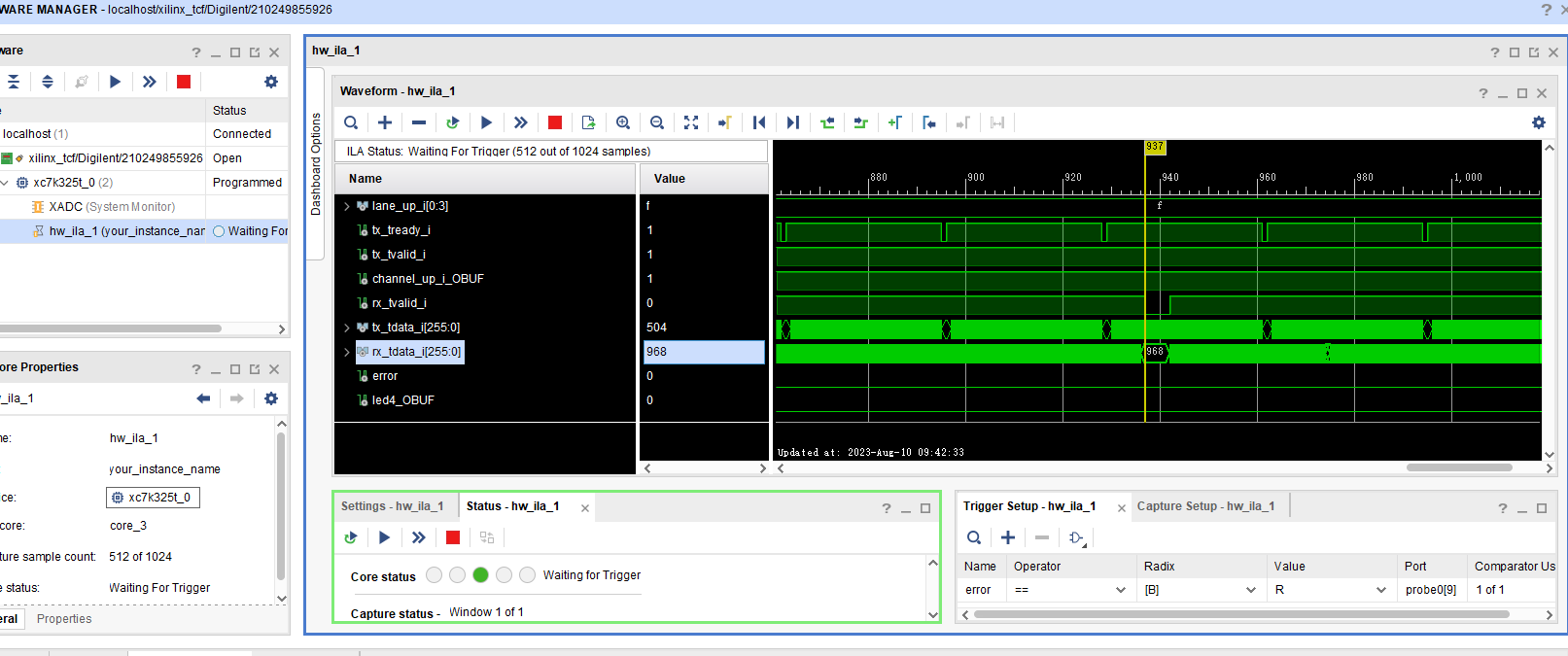

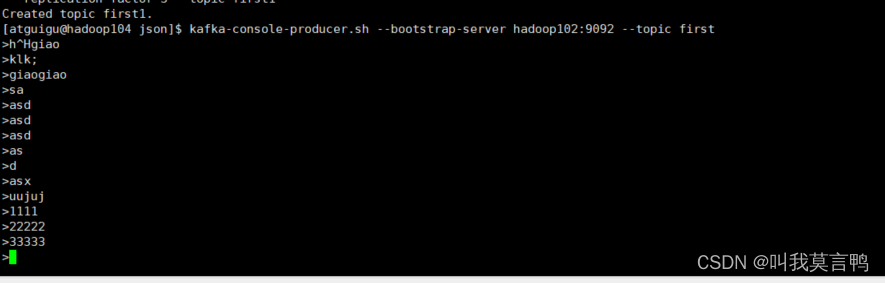

要在贴有K7系列FPGA芯片的板子和贴有KU系列FPGA芯片的板子之间通过光模块+光纤+QSFP+实现40G的高速通信。可以选择的方式有多种,但本质的方案就一种,即实现4路GTX与GTY之间的通信。可以选择8B/10B编码通过GT IP核实现,而不能通过Aurora 8/10BIP,因为KU系列中没有Aurora 8B/10B IP。由于8/10B编码方式要比64/66B编码方式传输效率低,所以这里选择64/66B编码方式。如果使用GT IP核实现64/66B编码的二者通信,打开example design会发现KU系列的例程只发送了PRBS序列进行验证,因此换成自己的数据做通信并不方便。此外GT IP核的侧重点是协议灵活,操作灵活,可以更多配置串行收发器“底层”的东西,而Aurora 64/66B对于没有太多特殊需求的用户显然是更友好的,将数据接口进行了封装,还可实现更高的传输效率,使用起来更为方便。由此最终选择Aurora 64/66BIP实现二者之间高达40G的传输。实际传输速度为10.3125Gbps*4=41.25Gbps。由于实现二者之间的通信并不太容易,因此此处构建一个简单的场景先进行原理验证,具体是是,在链路初始化完成之后,GTX向GTY发送0-1000的数字,GTY接收后检错并通过led表示;同时GTY也向GTX发送0-1000的数字,也是接收后检错并通过led表示。对应例程链接本次工程用到的是自己设计的板卡,连接方式如下图所示:

2.结构

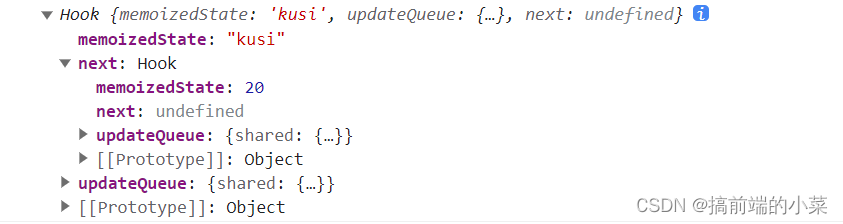

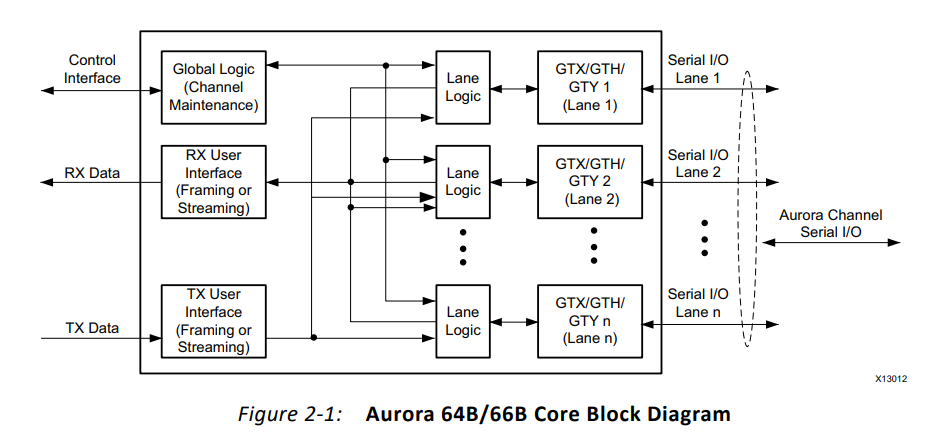

其内部模块以及通道模型与Aurora基本一致。

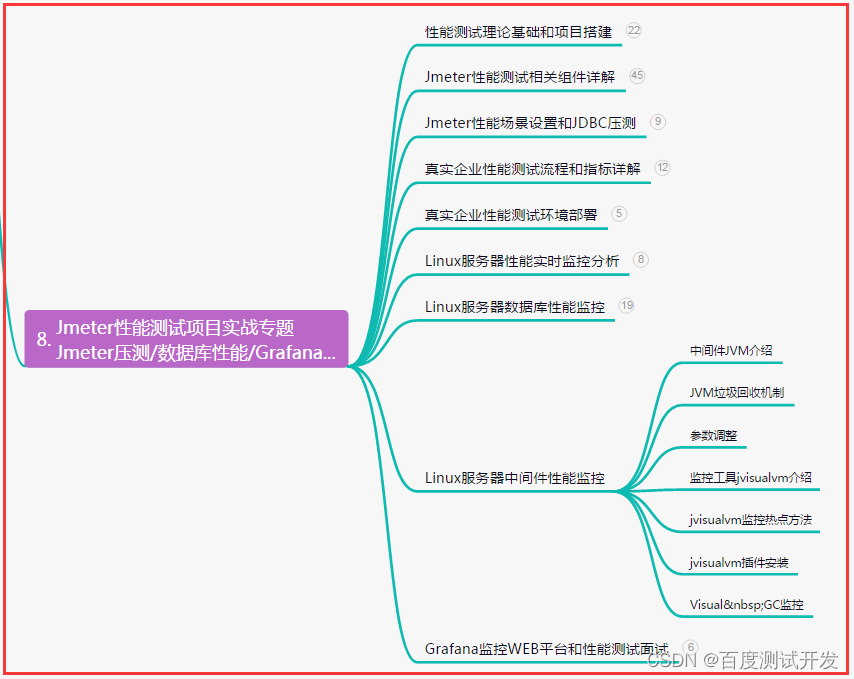

3.IP配置

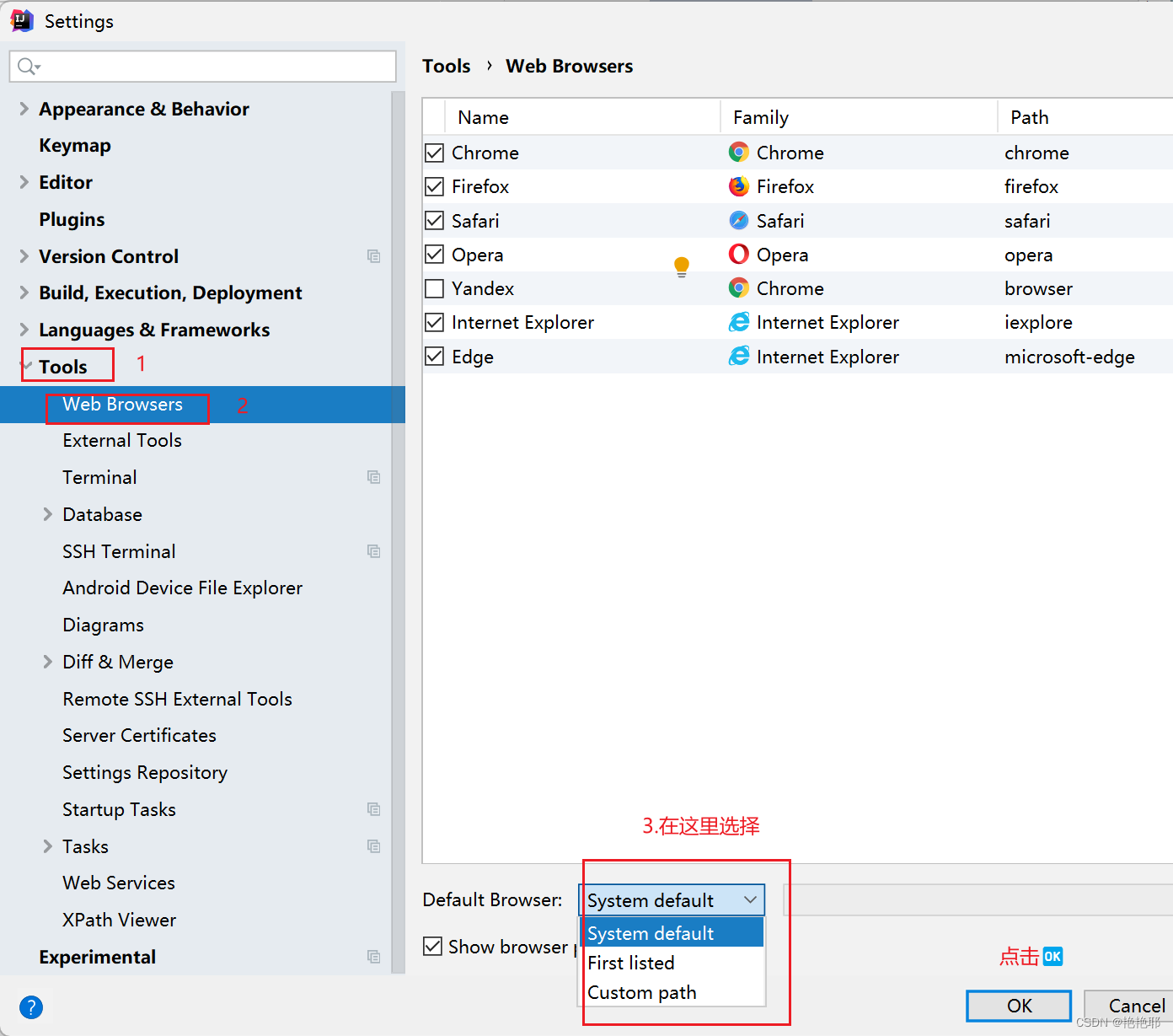

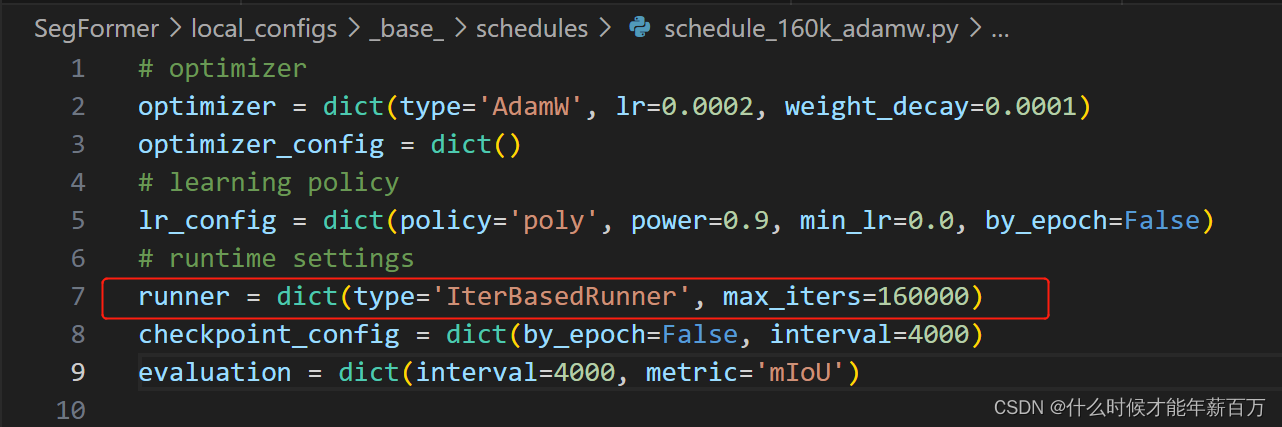

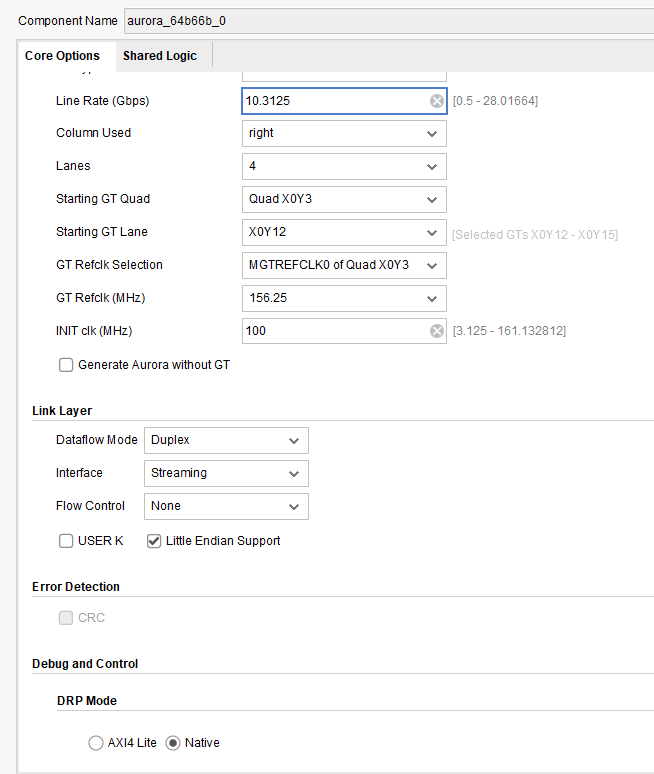

Aurora 64/66B IP核的配置与Aurora 8B/10B IP的配置基本一致,请参考Aurora 8/10Bip核实现。需要说明,此处GTX与GTY的IP核应配置成一样的速率,并选择同样的接口形式,为了区别于Aurora 8B/10B,此处选择streaming接口,同样都勾选小端模式,符合习惯。具体配置如下:

4.注意事项

①该IP核对复位逻辑有着较为严格的要求,如果工程需要复位,需要查看手册并按照时序要求配置相关信号;如果没有太多要求,可直接使用example design中的复位逻辑。

②用户时钟的计算,每路带宽10.3125Gbps,一共思路,因此总带宽是10.3125G*4=41.25Gbps,结合编码方式应该乘64,除66,然每一个周期发送的数据位宽是256bit,因此user_clk_i=41.25Gbps*(64/66)/256bit=156.25Mhz。

③GTX和GTY生成的例程略有不同,还要注意约束文件的修改。

④提供的例程源码是对example design做了一定的整理,仅仅为了美观。

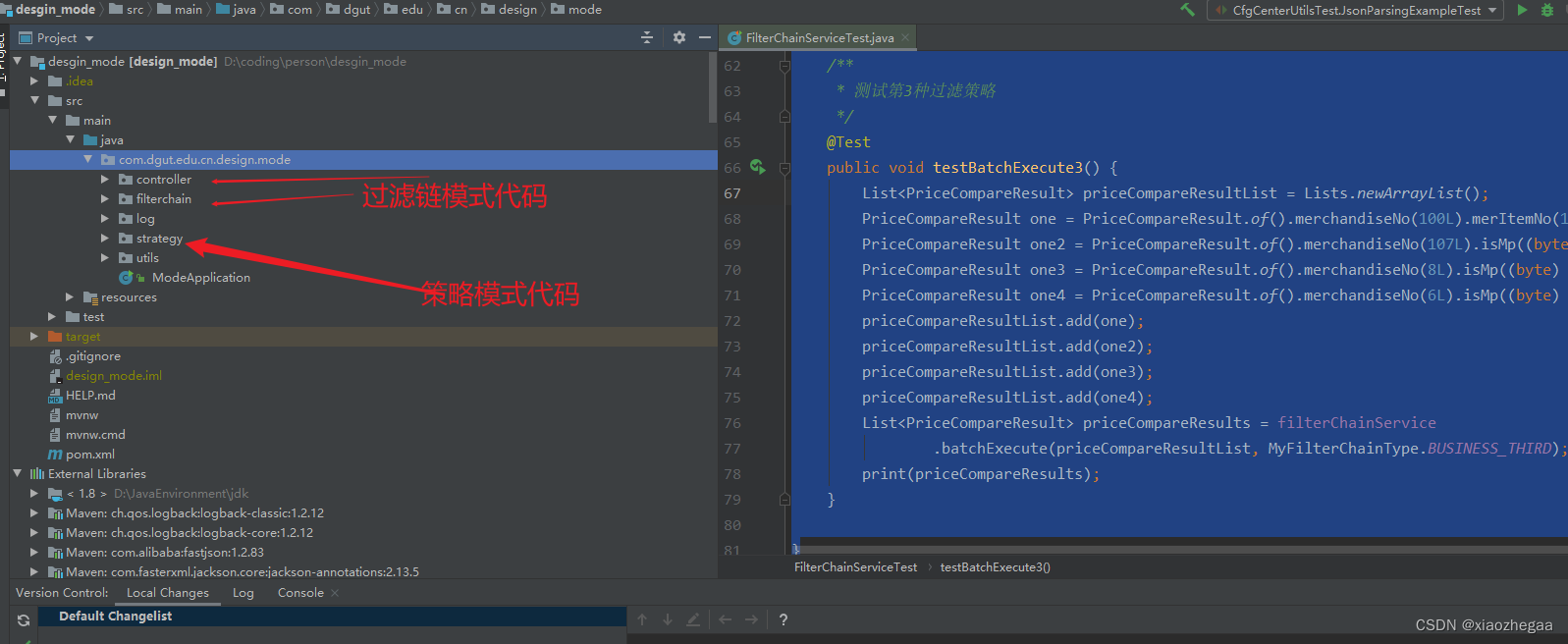

5.部分源码设计

发送端源码设计

module GTY_Xfer(input user_clk_i,input system_reset_i, //高电平复位input channel_up_i,input tx_tready_i,output reg[255:0]tx_tdata_i,output reg tx_tvalid_i);wire local_rst;

assign local_rst = system_reset_i | !channel_up_i;

always @(posedge user_clk_i or posedge local_rst) beginif(local_rst == 1)begintx_tvalid_i <= 0;end else begintx_tvalid_i <= 1;end

end

always @(posedge user_clk_i or posedge local_rst) beginif(local_rst == 1)begintx_tdata_i <= 0;end else if(tx_tready_i)begintx_tdata_i <= tx_tdata_i + 1;if(tx_tdata_i == 1000)begintx_tdata_i <= 0; end end

end

endmodule接收check源码

module GTY_Recv(input user_clk_i,input system_reset_i, //高电平复位input channel_up_i, input [255:0] rx_tdata_i,input rx_tvalid_i,output reg led4,output error );wire local_rst;

assign local_rst = system_reset_i | !channel_up_i;

reg [255:0]rd_cnt;

always @(posedge user_clk_i or posedge local_rst) beginif(local_rst == 1)beginrd_cnt <= 0;end else if(rx_tvalid_i)beginrd_cnt <= rd_cnt + 1;if(rd_cnt == 1000)beginrd_cnt <= 0;endend

end

assign error = rx_tvalid_i & (rd_cnt != rx_tdata_i);

always @(posedge user_clk_i or posedge local_rst) beginif(local_rst == 1)beginled4 <= 0;end else if(error)beginled4 <= 1;end

end

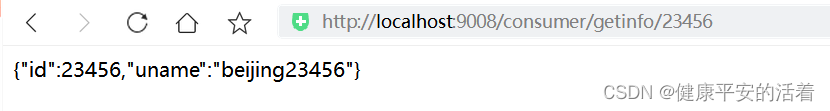

endmodule6.效果

在两端均可抓取到正确的数据信号,并且无error产生。