目录

一.实验目的

二.实验仪器设备

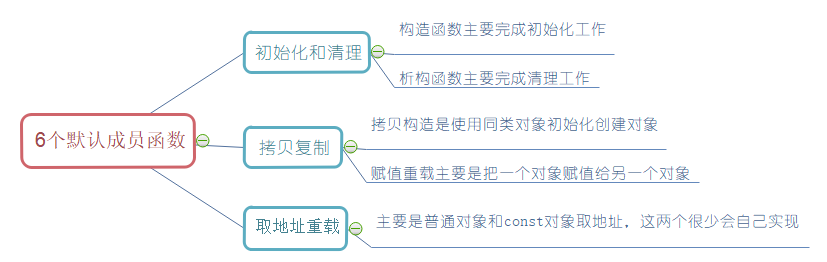

三.实验原理:

四.实验要求

五.实验内容及步骤

1.实验内容

2.实验步骤

六.实验报告

七.实验过程

1.创建Verilog文件,写代码

2.波形仿真

3.作出电路图

4.烧录文件

一.实验目的

1.了解4选1的工作原理和实现的方法。

2.实现4选1多路选择器。

3.学会用于Verilog语言进行程序设计。

二.实验仪器设备

1.PC机一台

2.FPGA实验开发系统一套。

三.实验原理:

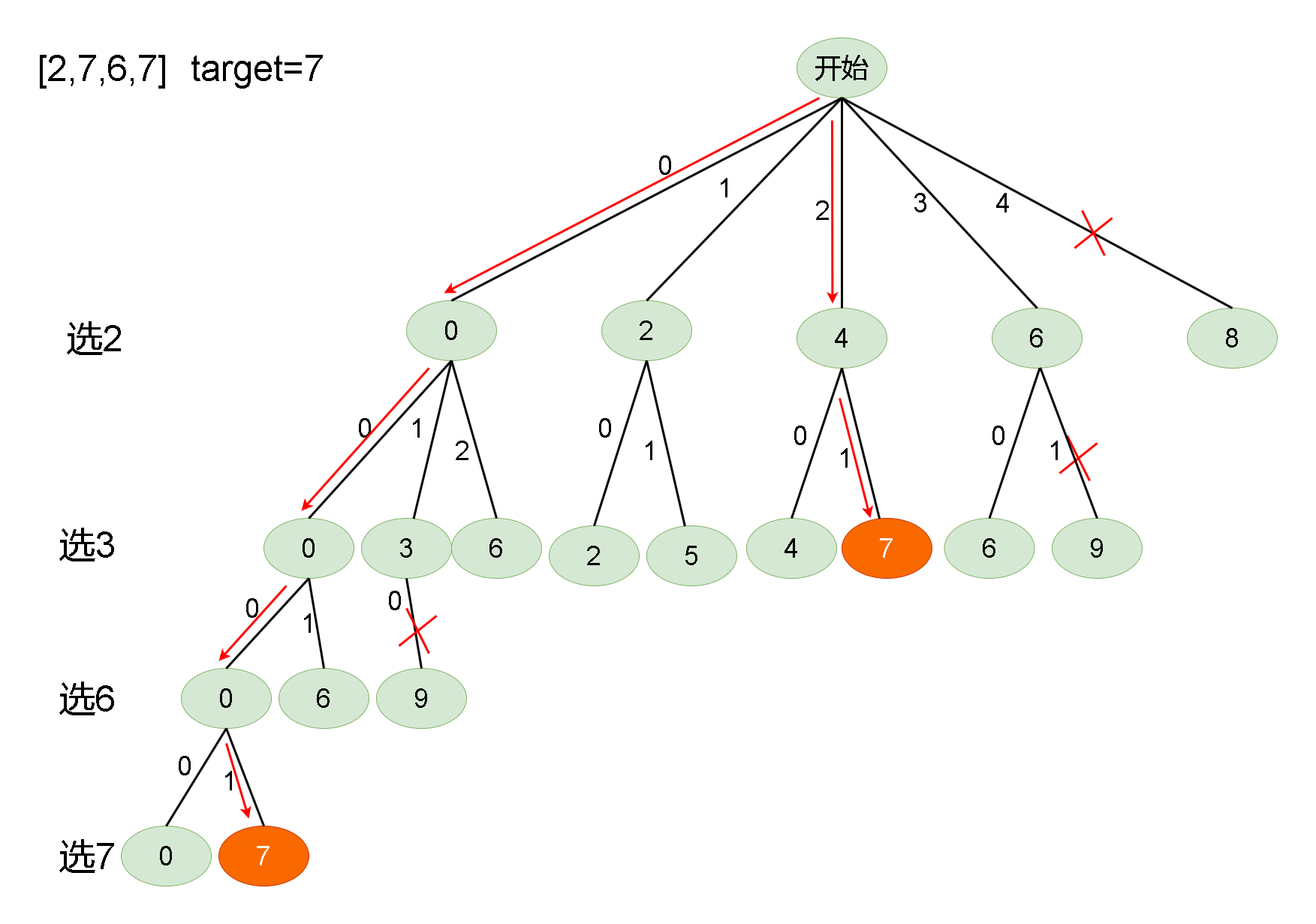

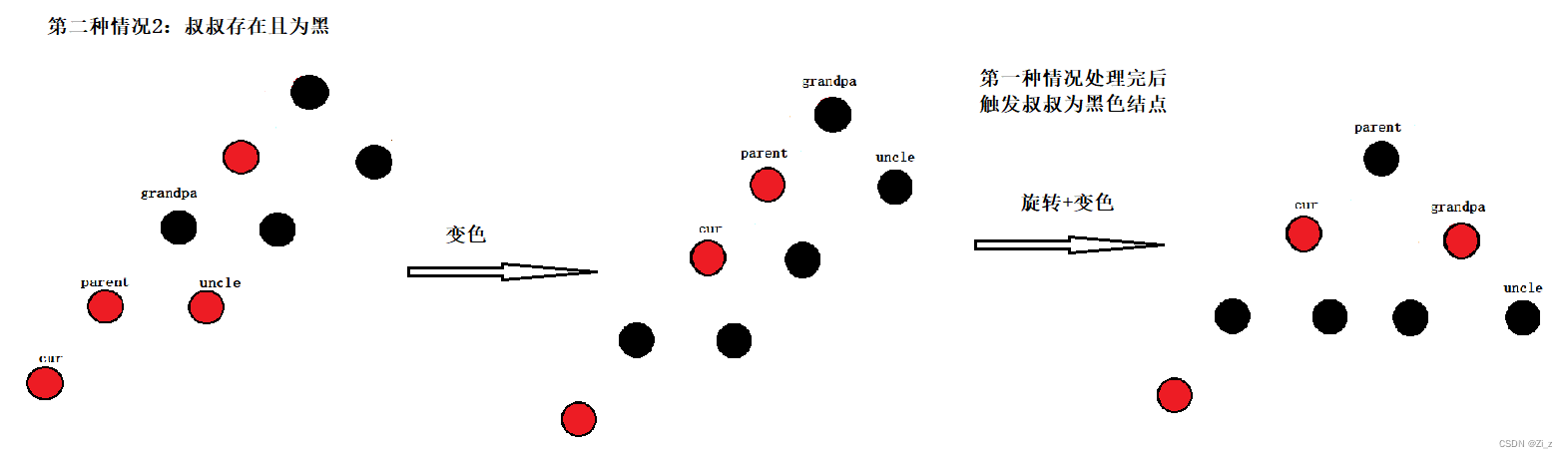

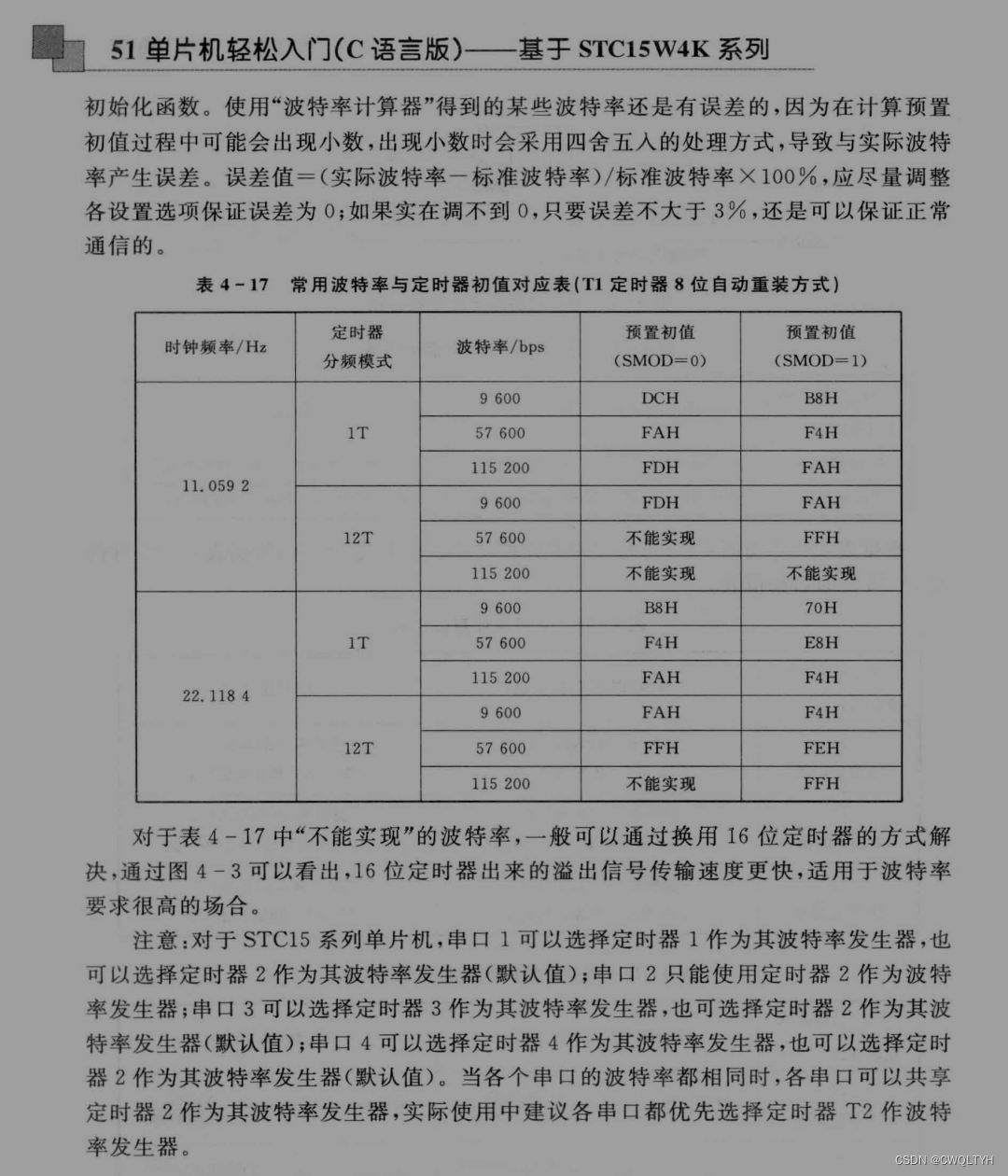

4选1对应的功能真值表如下图:

当选择输入AB为LL时,Y输出D0, 当AB为LH时,Y输出D1, 当AB为HL时,Y输出D2,当AB为HH时,Y输出D3。

四.实验要求

1.预习教材中的相关内容。

2.阅读并熟悉本次实验的内容。

3.用Verilog语言完成4选1多路选择器电路设计。

五.实验内容及步骤

1.实验内容

分别采用case语句表达式、assign语句表达式、条件赋值语句表达式、条件语句表达式(if)设计4选1多路选择器。选择其中一种方法下载到板子验证即可,其余在仿真验证。

2.实验步骤

(1).开机,进入QUARTUSⅡ软件系统。

(2).建立工程。主芯片为Cyclone2系列EP2C20Q240C8N型号。工程名为

MUX41a。

(3).新建一个Verilog HDL File文件,命名为MUX41a.v。

(4).使用Verilog语言编写4选1多路选择器。

(5).保存文件。

(6).将MUX41a.v文件设置为工程的顶层文件并编译。

(7).创建仿真文件University Program VWF,添加所需的变量并进行功能仿

真。

(8).分析仿真结果

(9).配置管脚(四个按键分别是(153,95,154,31),拨码开关接(212,213),

LED接(218))

(10).编译综合下载验证。

六.实验报告

1.总结Verilog设计多路选择器使用的最基本与核心的语法知识。

2.对仿真的结果进行分析。

3.讨论自己在设计过程中遇到的问题、解决的过程以及收获体会。

七.实验过程

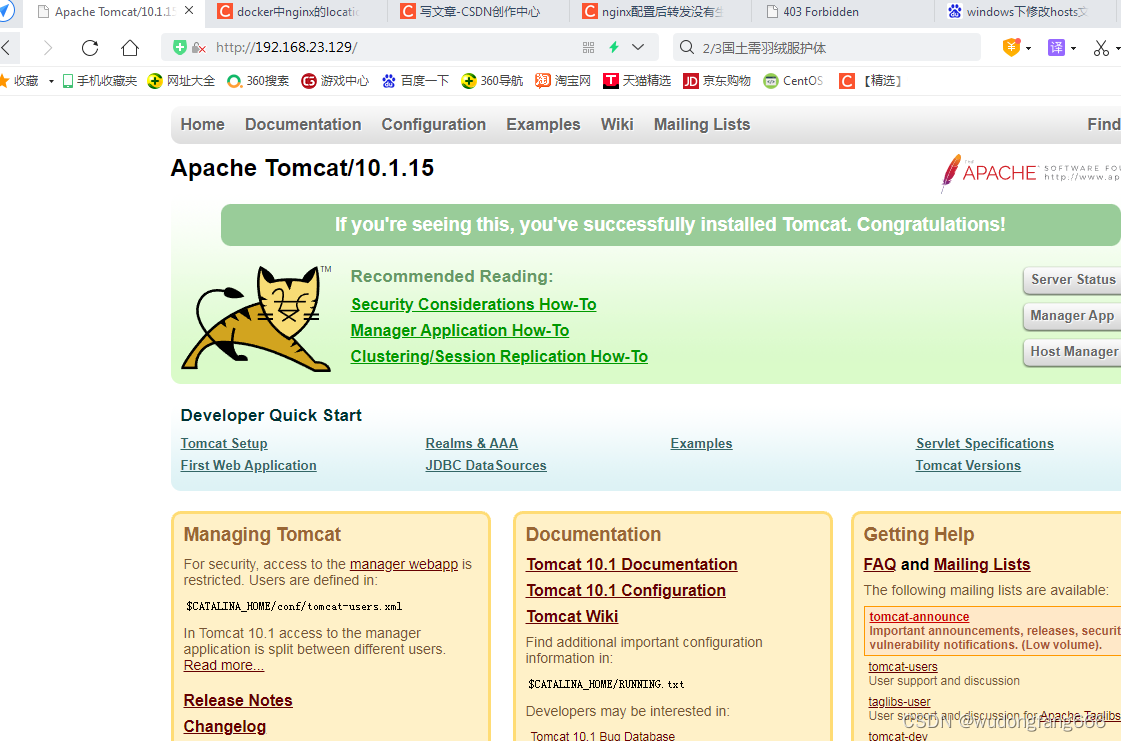

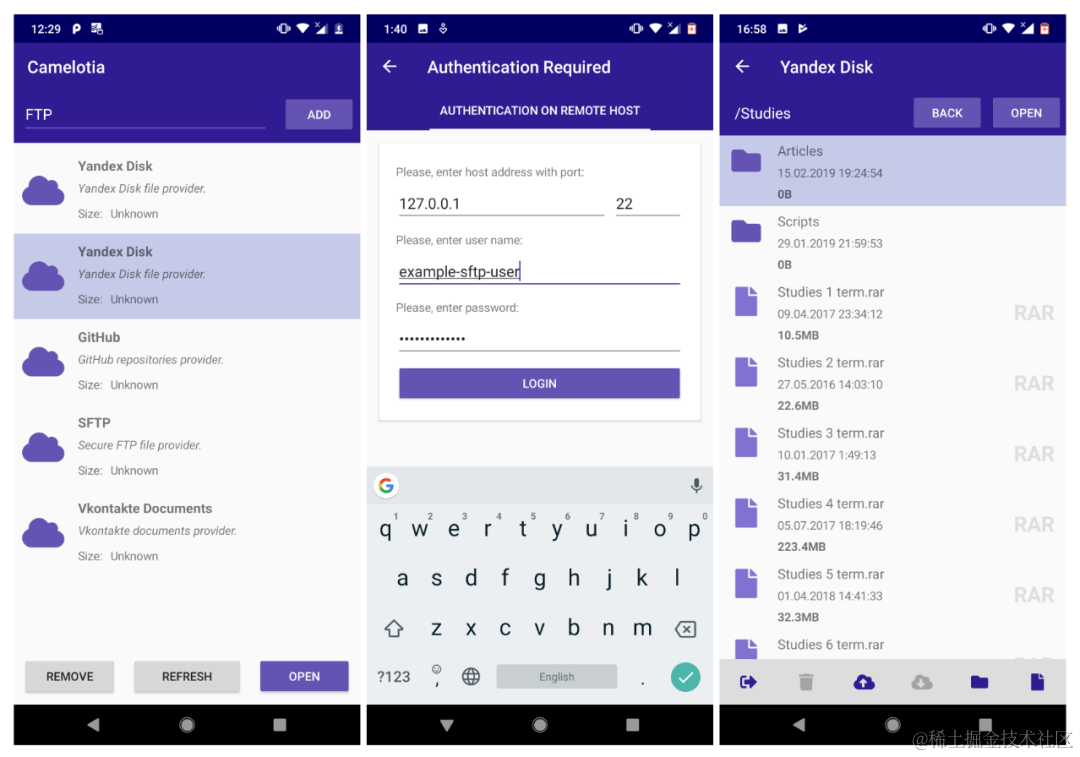

点击New project……创建新工程

然后设置项目的路径和名称(自己设置就好了)

选择相对应的芯片类型(看自己情况选择)

创建完成!

创建完成!

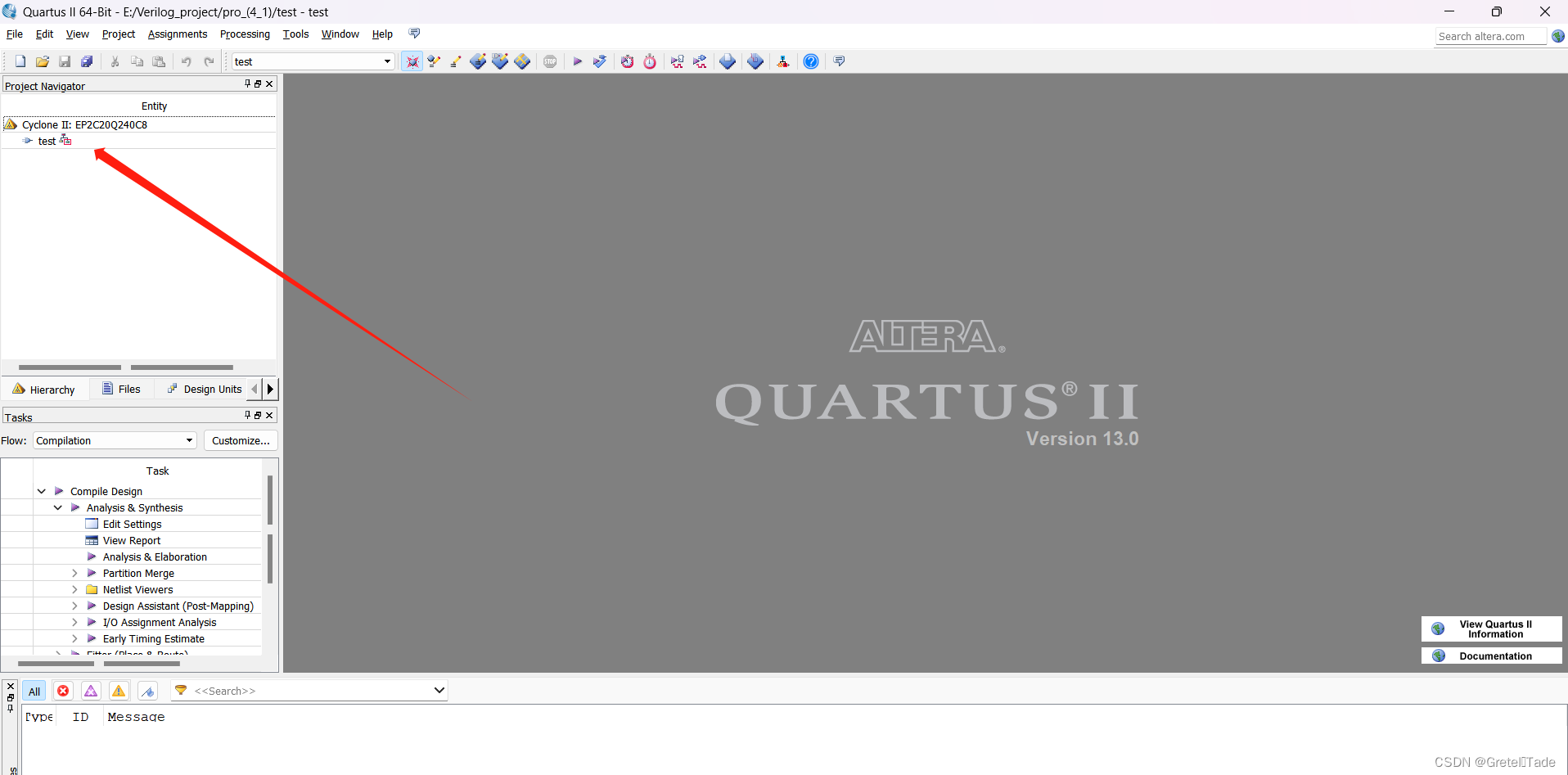

1.创建Verilog文件,写代码

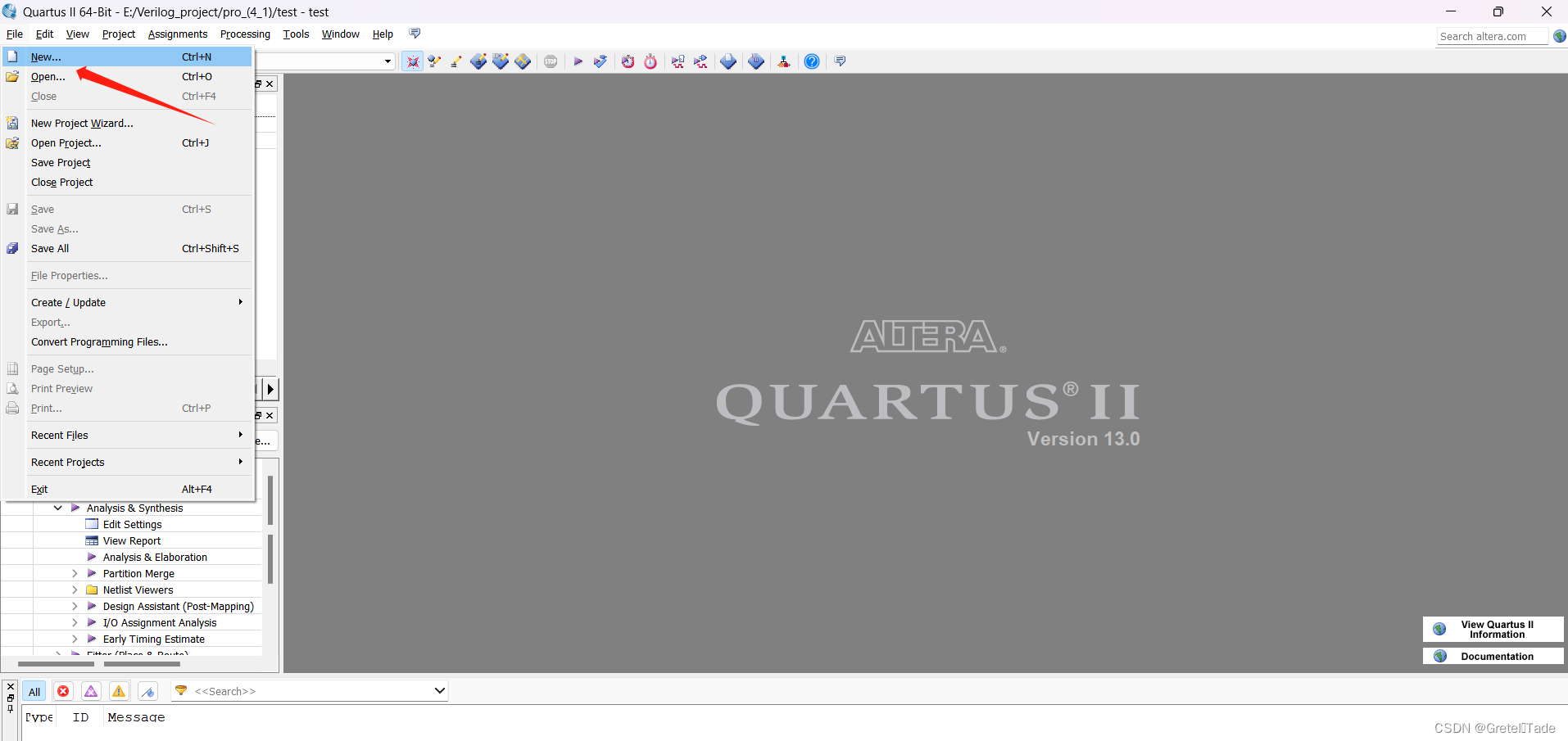

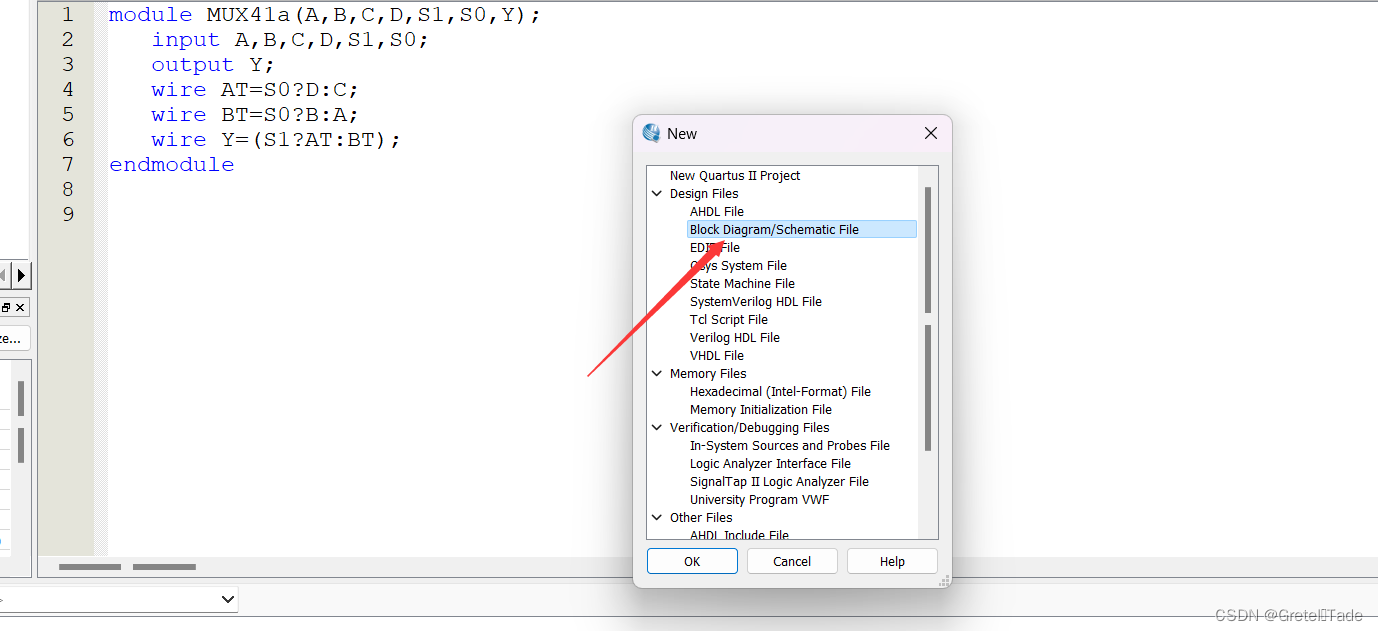

点击New,创建文件

选择Verilog文件,创建

选择Verilog文件,创建

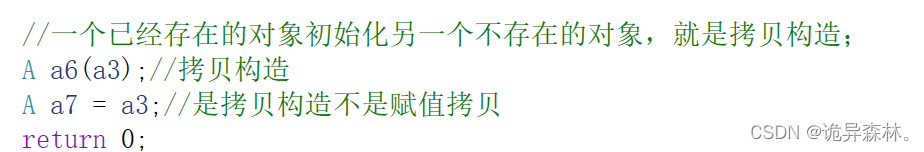

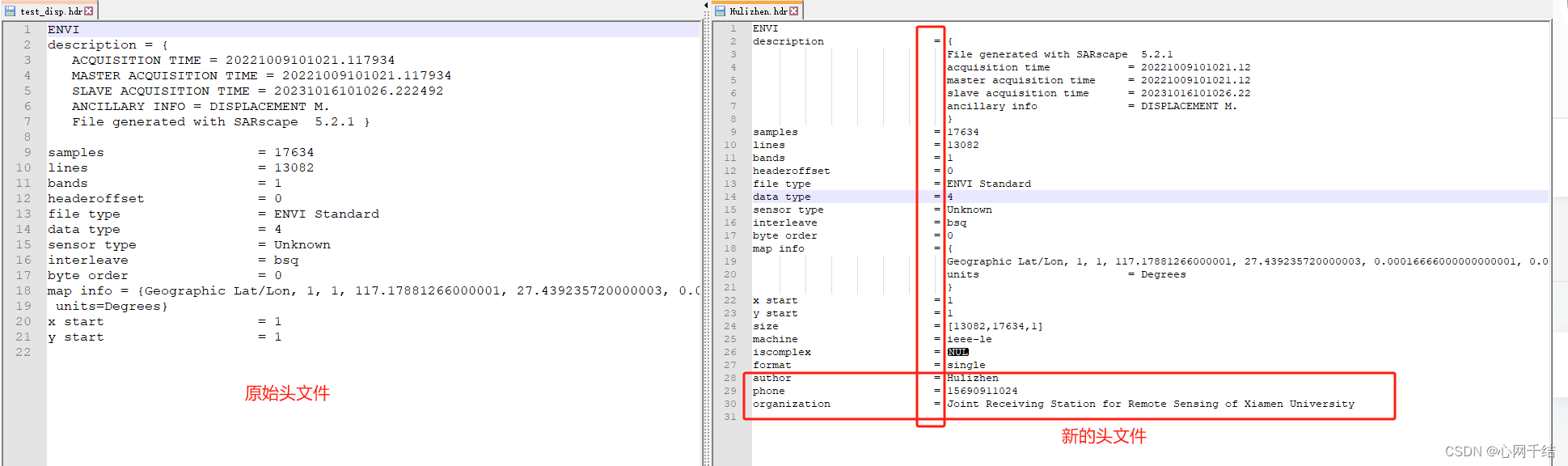

然后就是写代码,写完之后就进行保持文件,把文件的名称跟模块的名称改成一样。(必须一致)

代码如下:

module MUX41a(A,B,C,D,S1,S0,Y);input A,B,C,D,S1,S0;output Y;wire AT=S0?D:C;wire BT=S0?B:A;wire Y=(S1?AT:BT);

endmodule

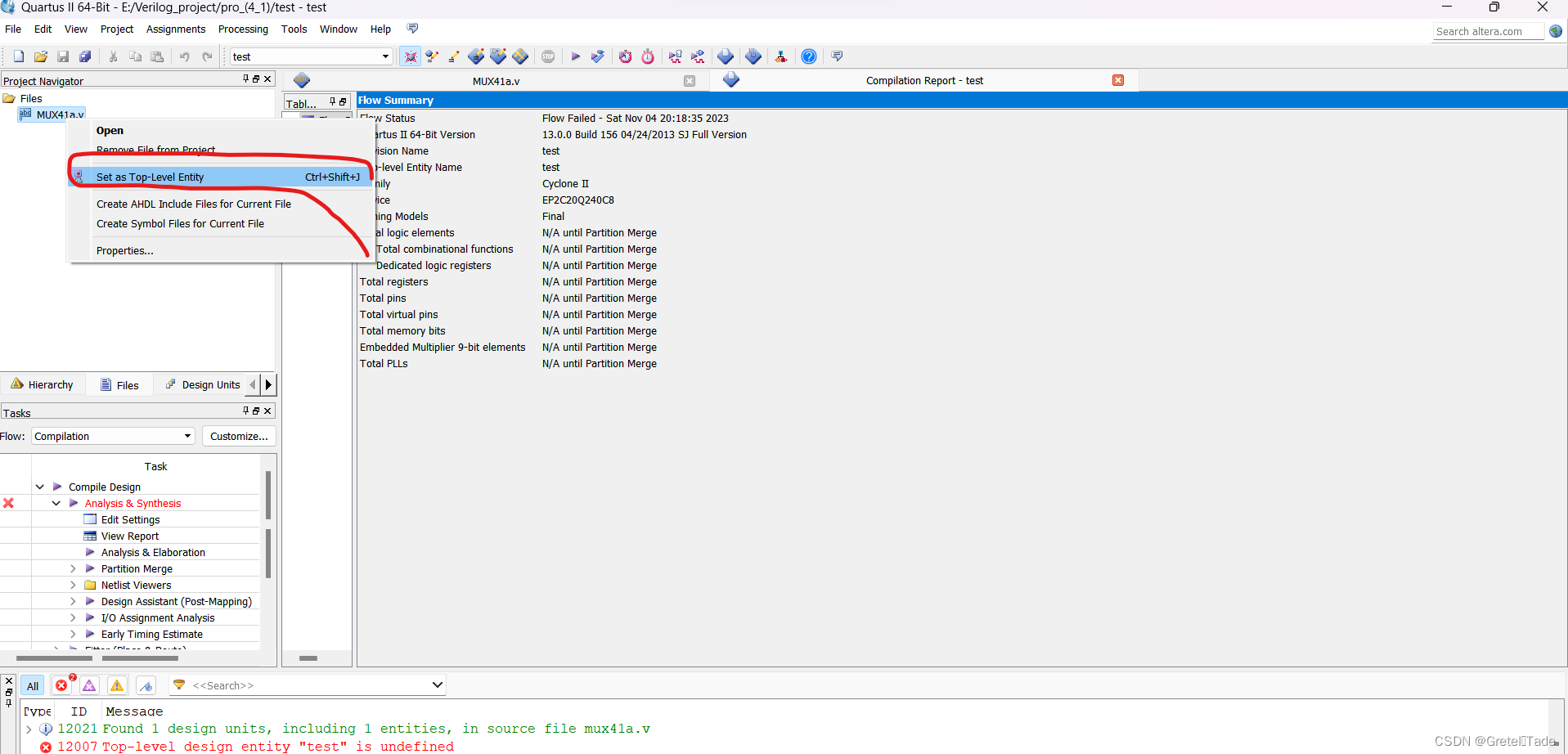

写好了之后就进行保存  然后,把这个文件设置为顶层文件,右键点击这个.v文件,然后如下图所示,点击设置顶层文件

然后,把这个文件设置为顶层文件,右键点击这个.v文件,然后如下图所示,点击设置顶层文件

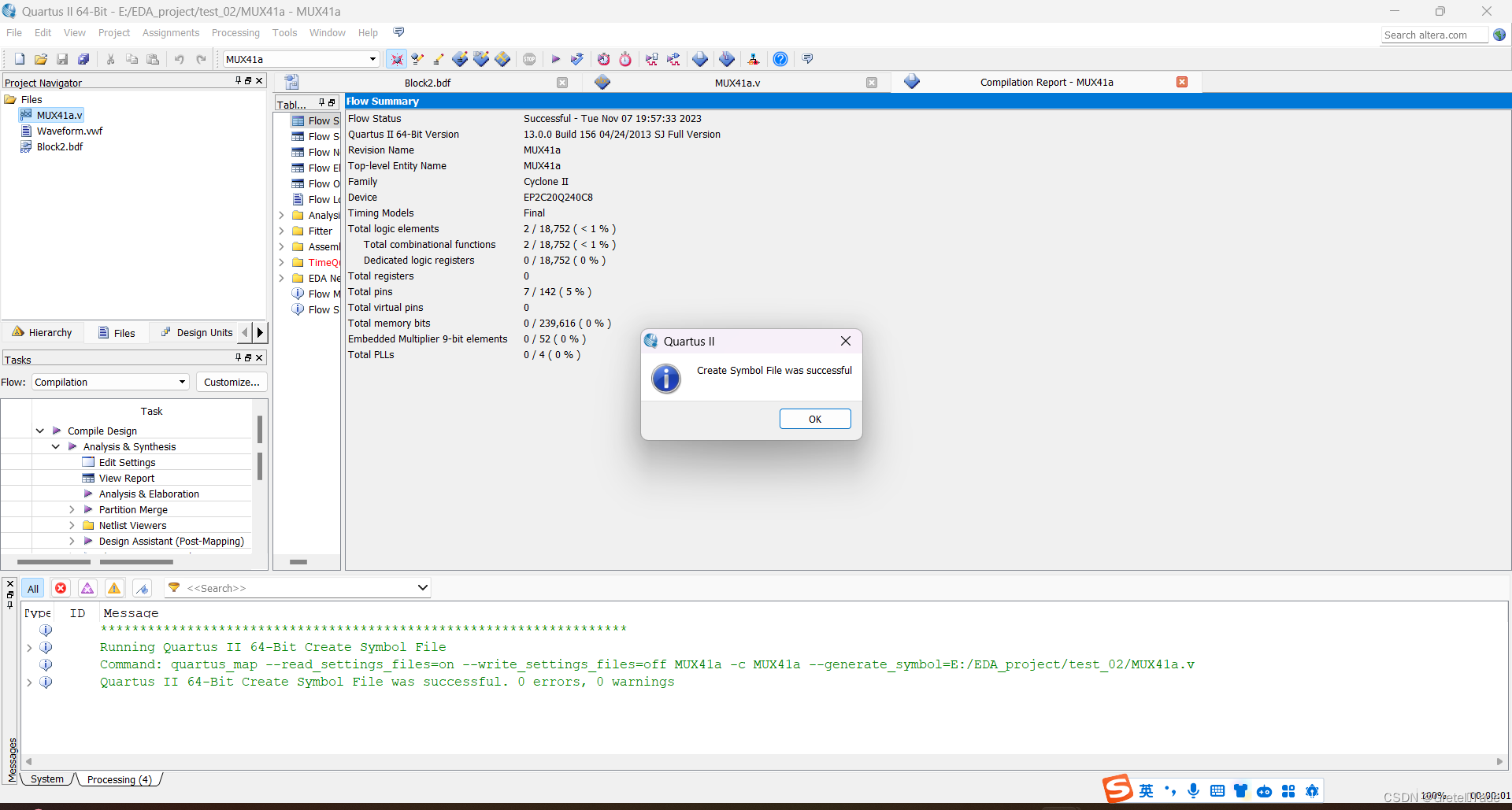

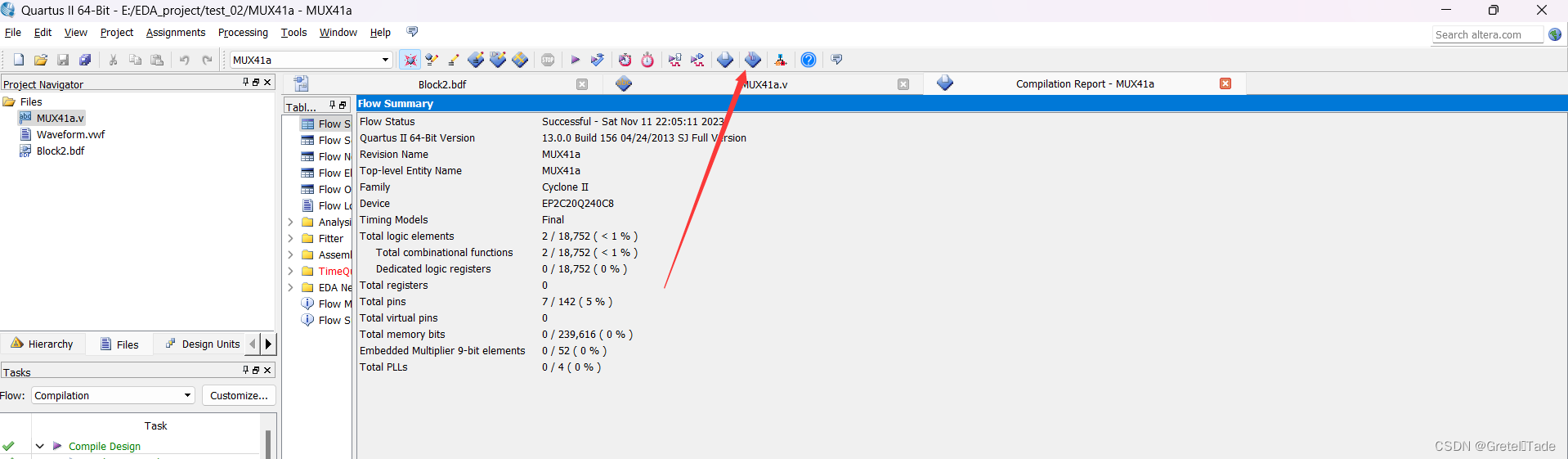

最后就是编译运行,如图所示,没有显示报错,就说明代码是没问题的。

2.波形仿真

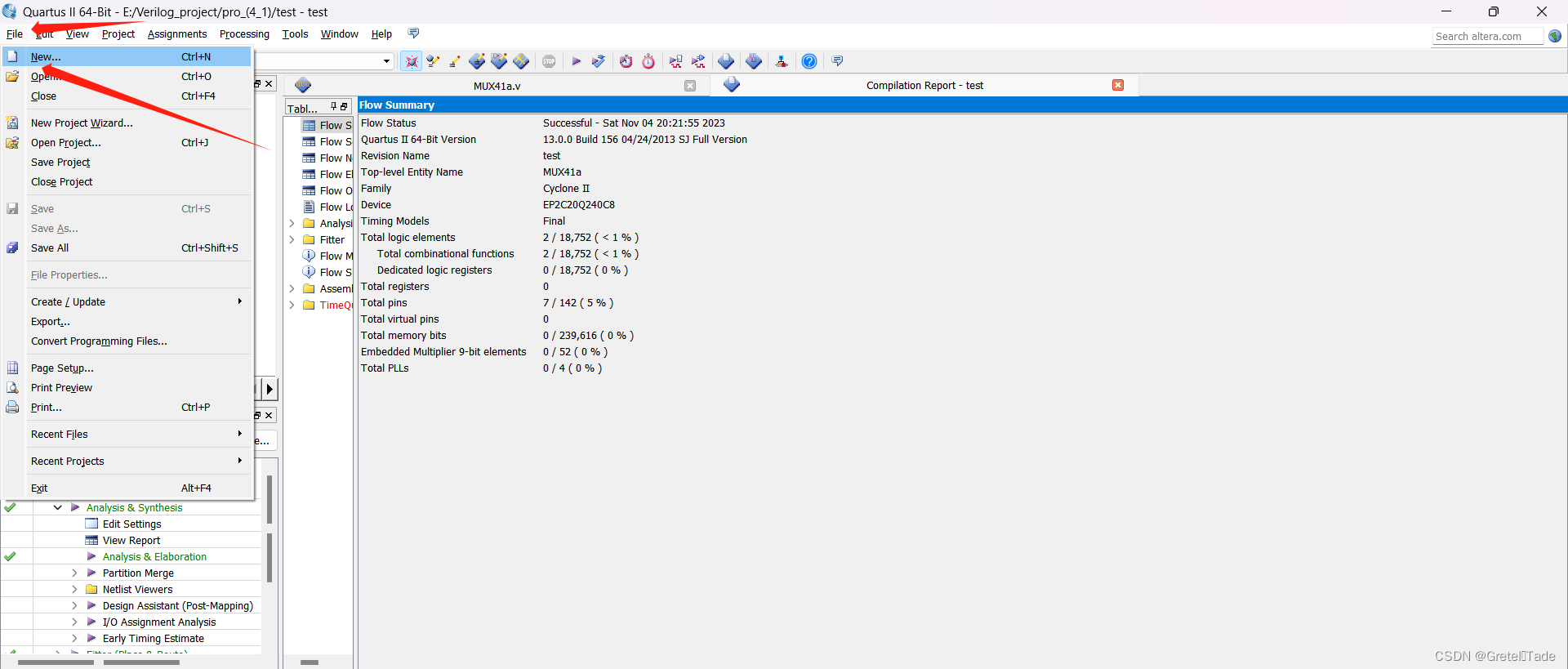

同样的,还是去点击新建文件

选择创建仿真文件:

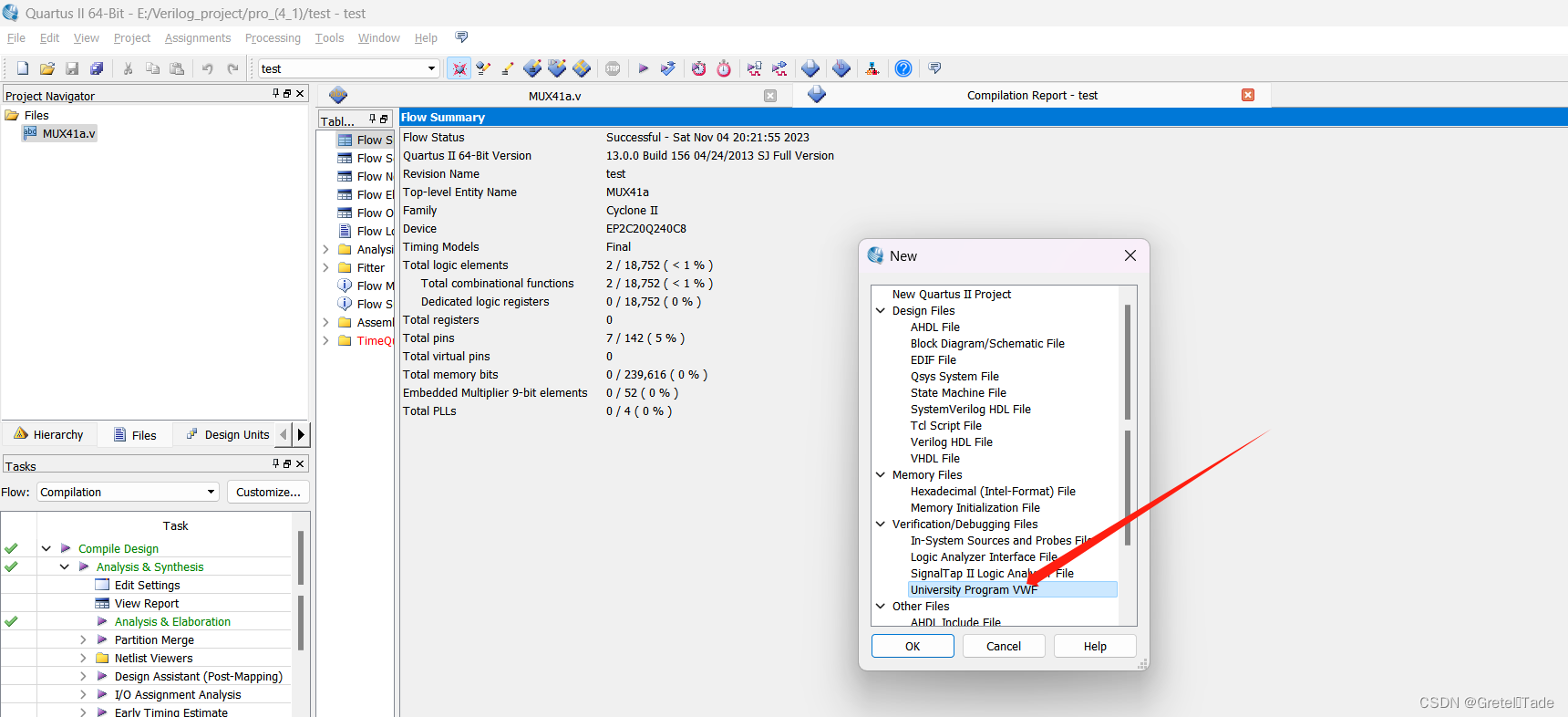

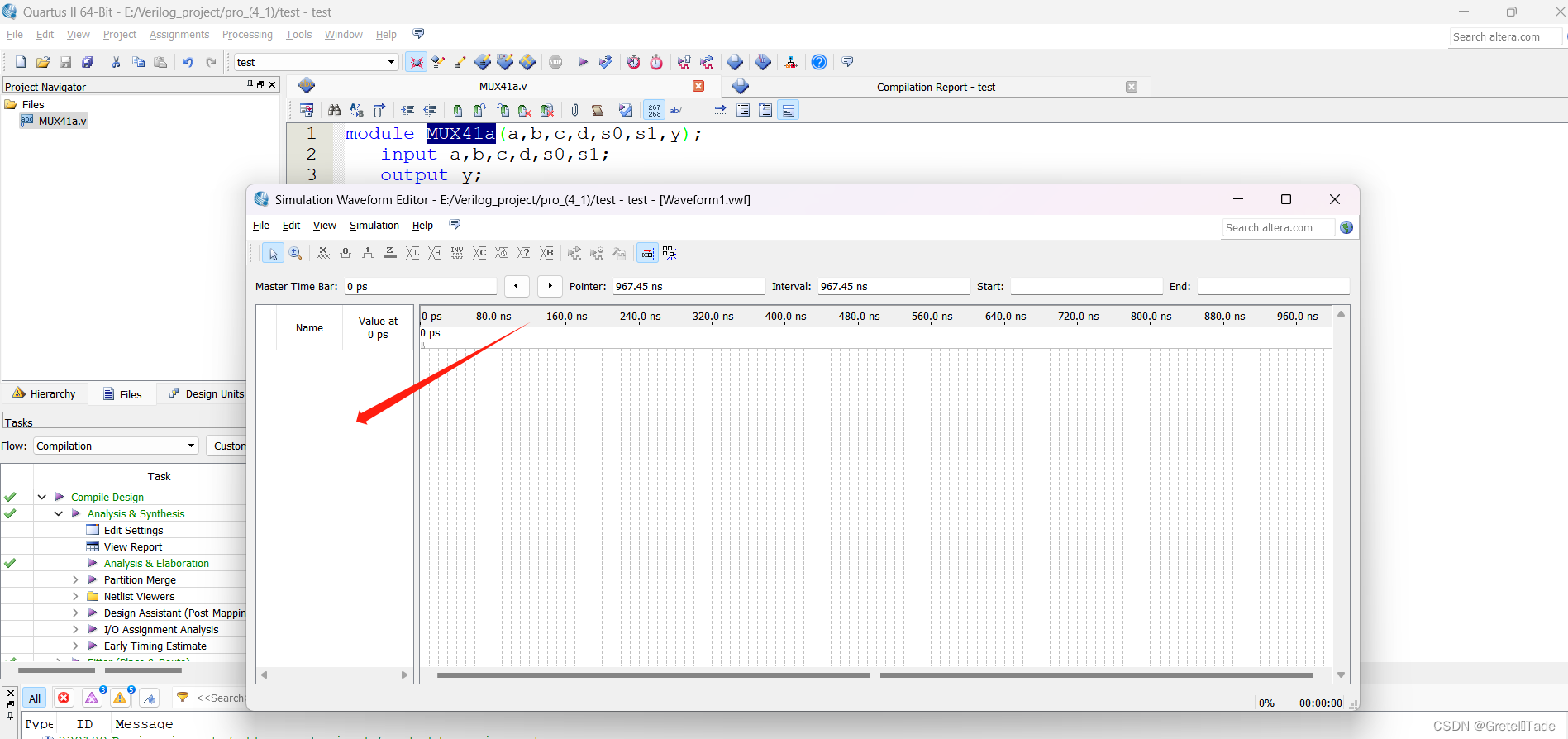

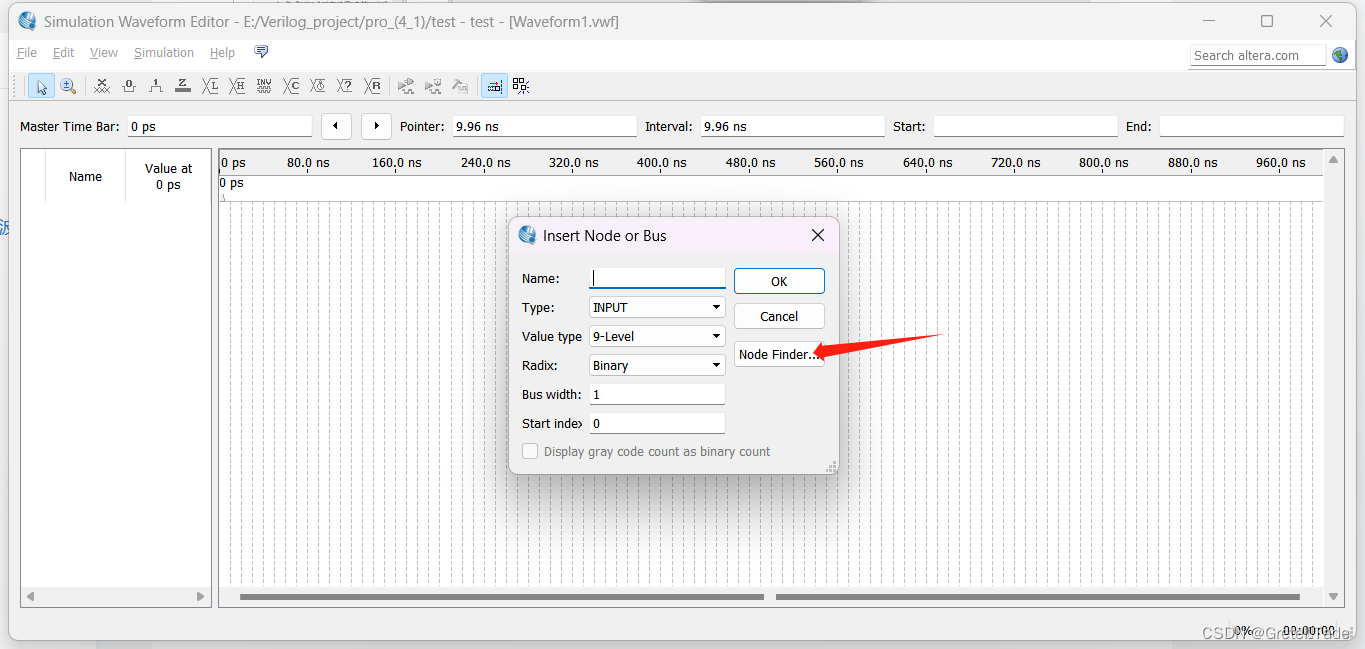

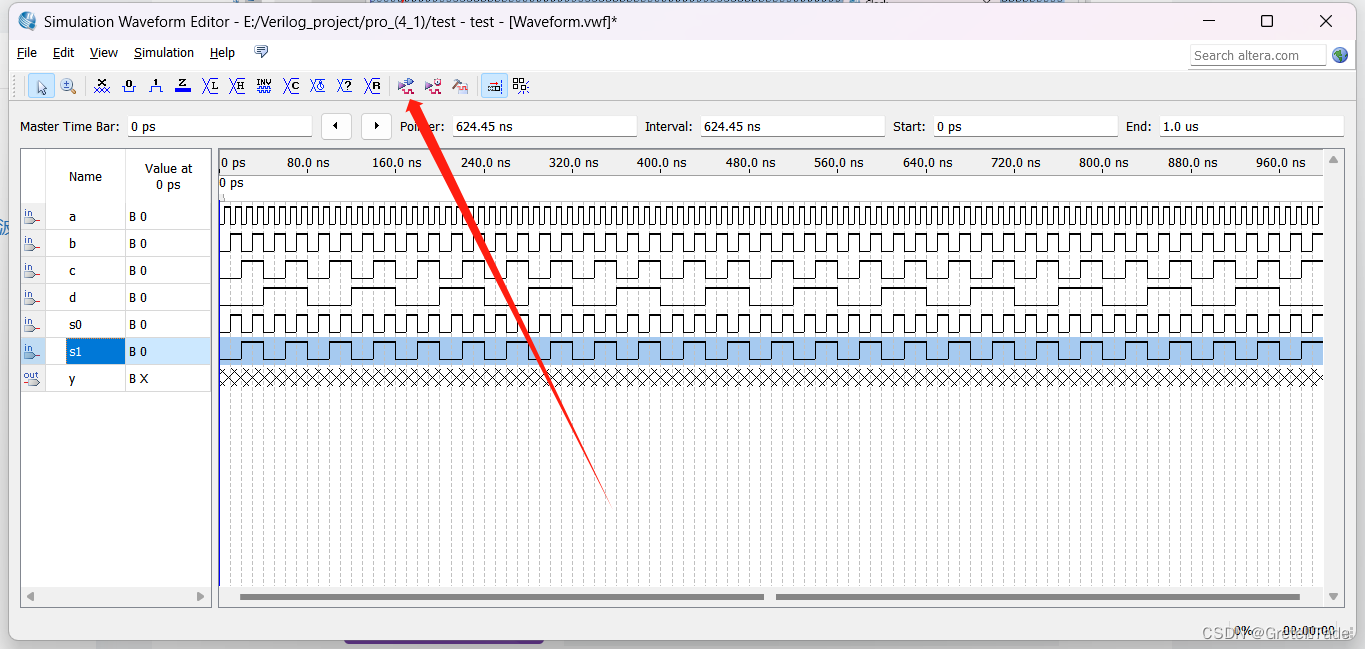

如图所示,鼠标双击下图红色箭头指向的位置,导入输入输出接口。

点击下图箭头指向的位置,导入接口设置。

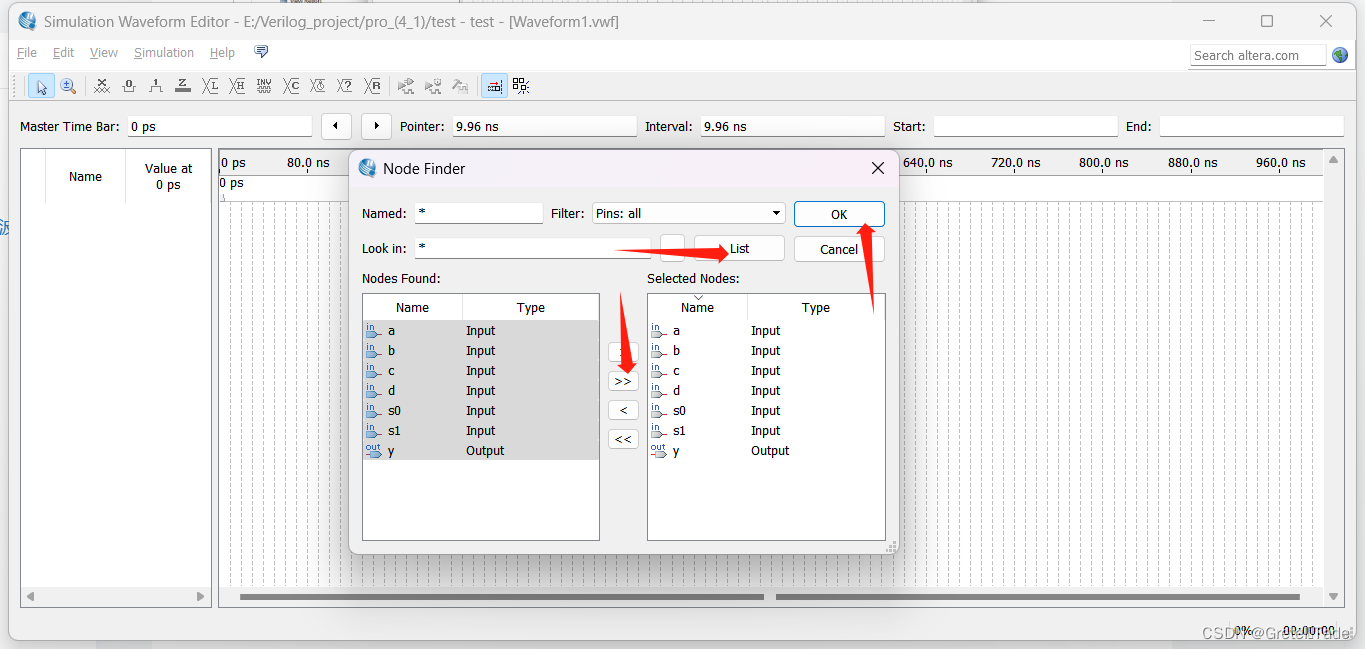

进去之后,点击List,显示接口,然后把接口右移到当前仿真文件当中,最后点击OK就行了。

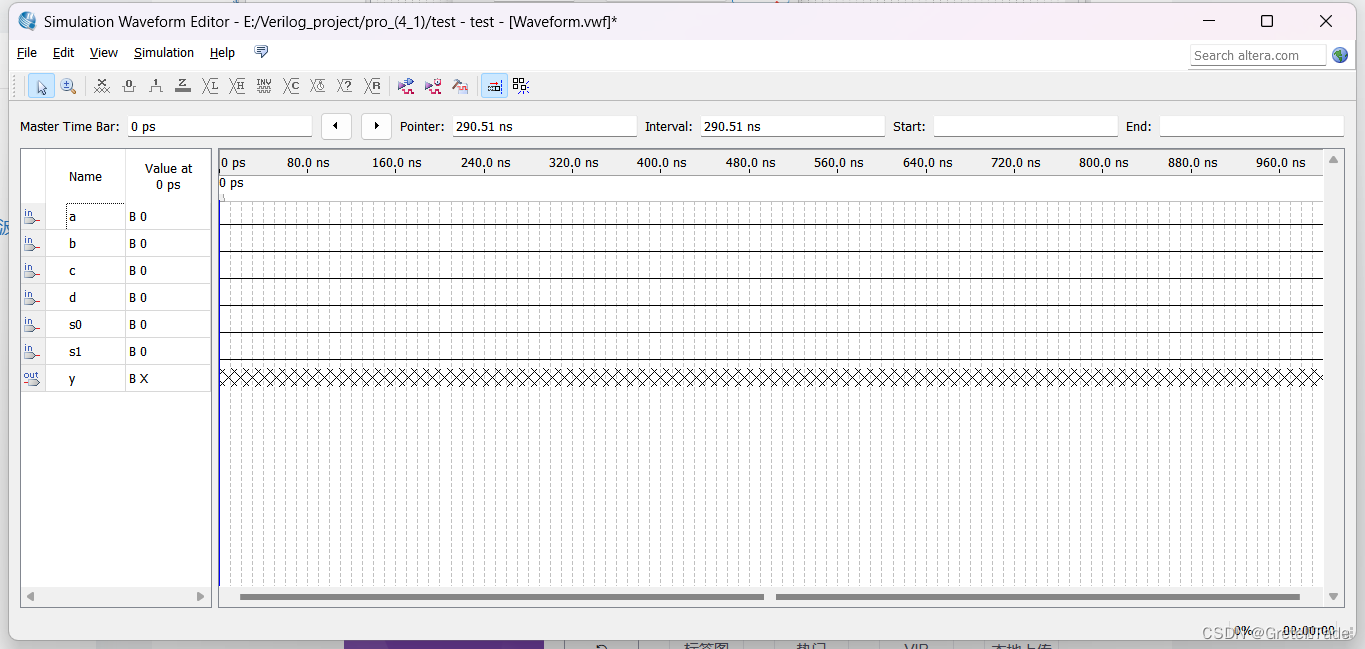

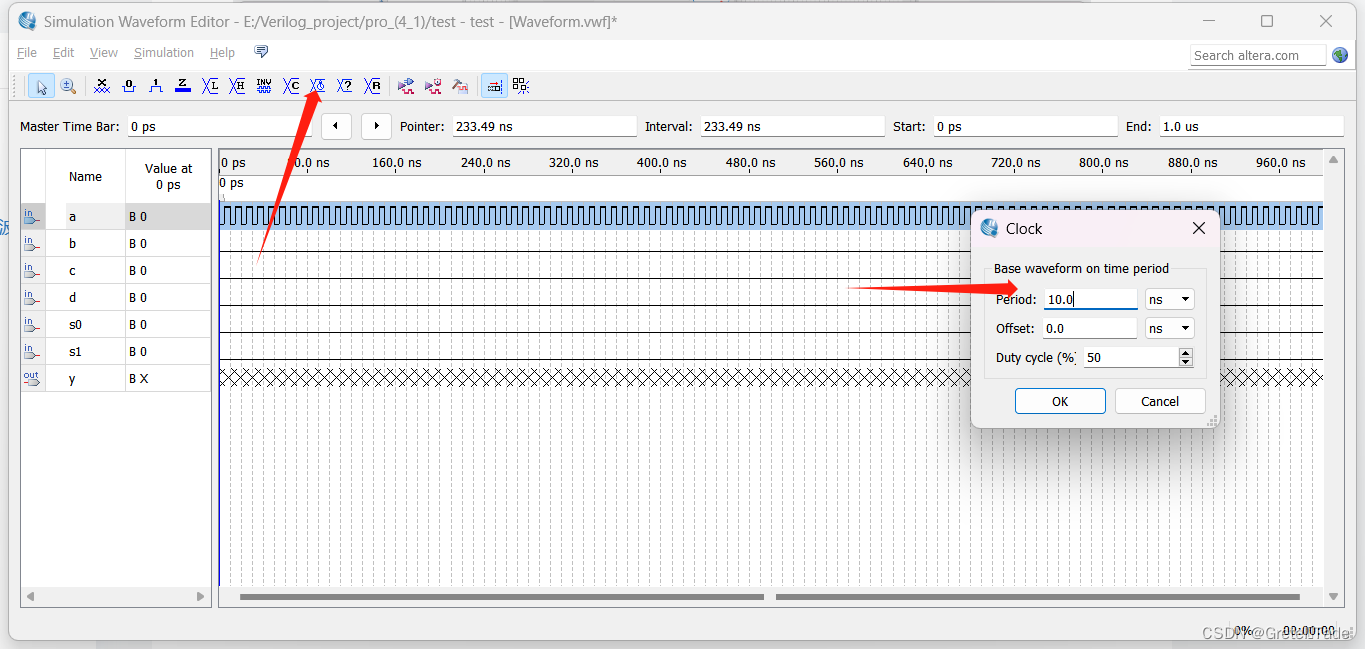

然后就是设置输入的波形,依次如下操作:

设置完成了之后,就进行编译运行

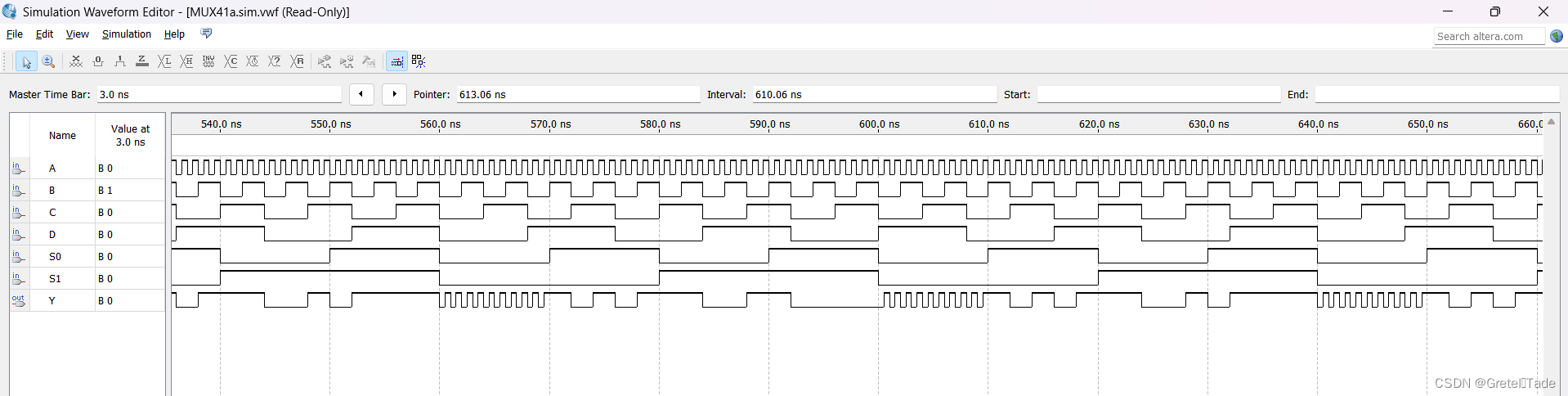

仿真结果如下:

然后对比相关逻辑,如果仿真无误就可以去画电路图了。

3.作出电路图

创建block文件,如图所示:

然后就是,点开左下方file文件,鼠标右键Verilog文件,然后生成子模块文件,如图所示:

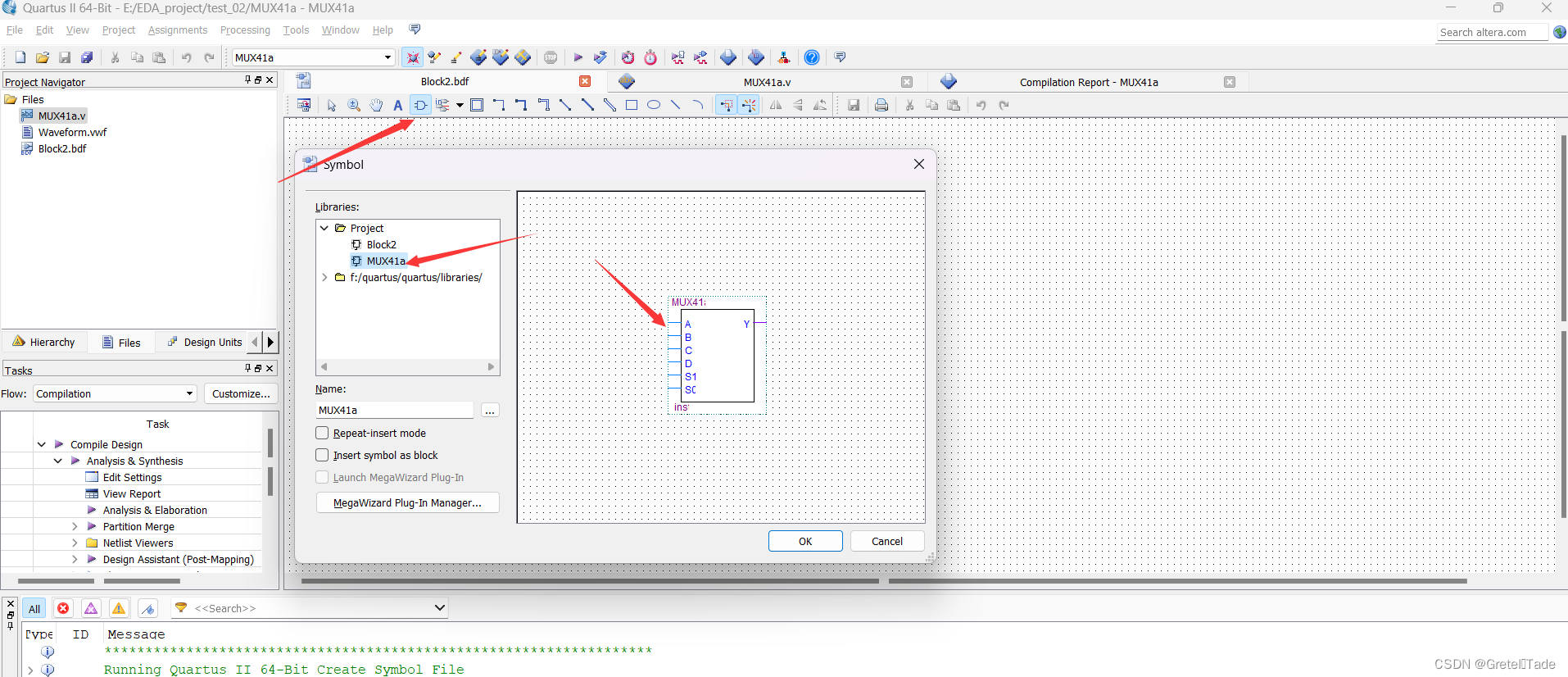

然后就是点开block文件,然后点击选择元器件,点开project文件夹,这里我们就会看到,有一个生成的元器件,也就是我们前面Verilog语言编程的元器件。

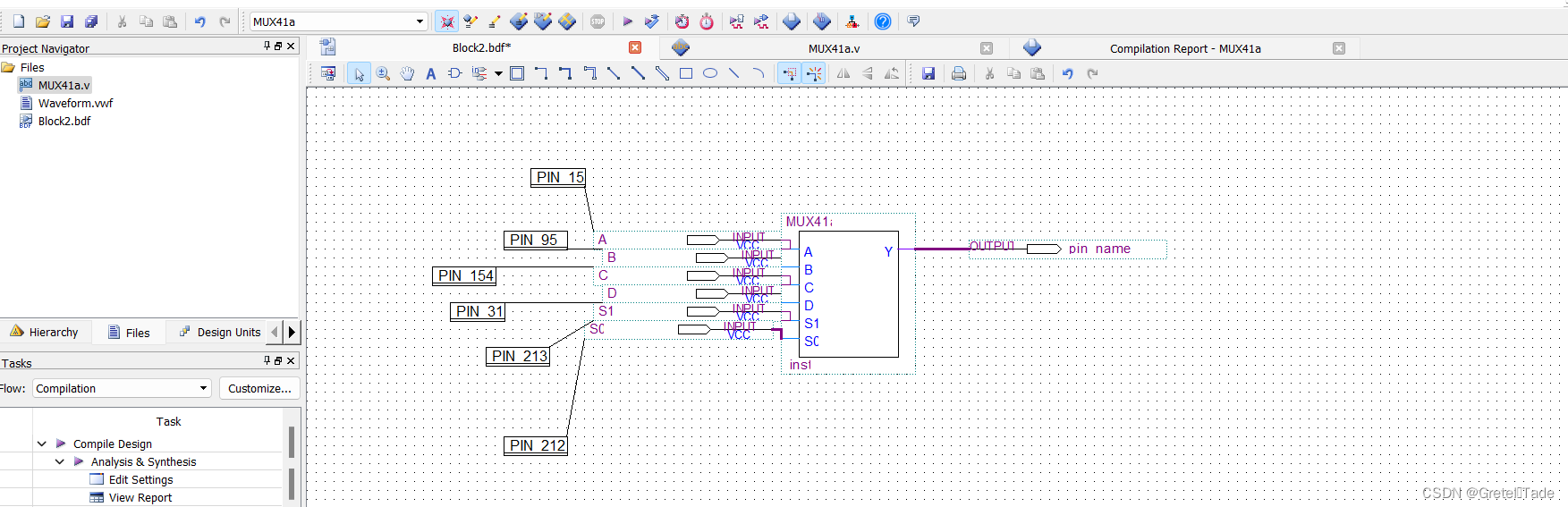

然后就可以去画电路图了。电路图如下所示:

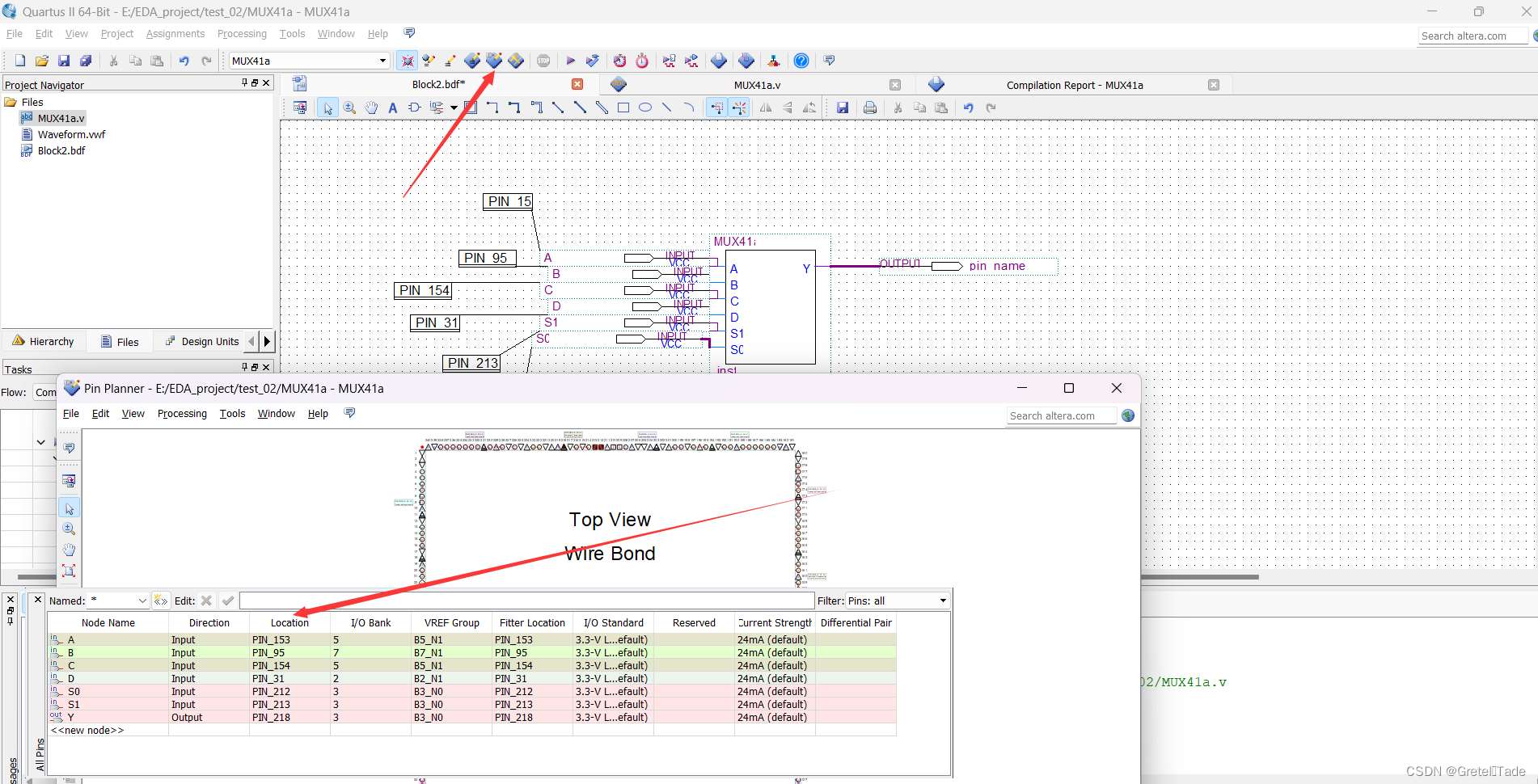

画好了电路图就进行引脚的绑定操作。如图所示,点开上面红色箭头指向的东西,然后下面就是去对每一个输入输出引脚去进行绑定。(根据实际情况需求去绑定)

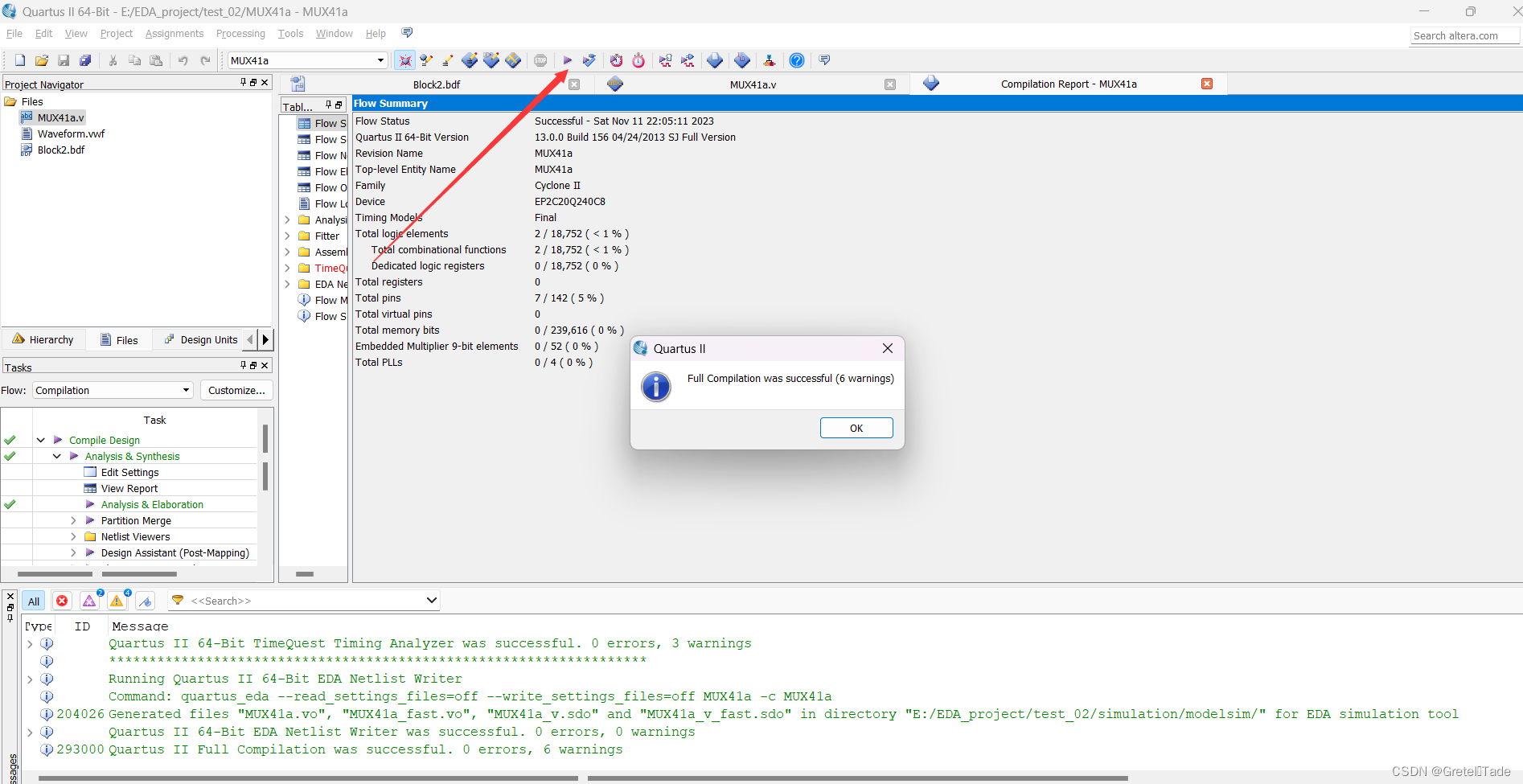

绑定完成了之后就是去编译运行,运行无错后就可以进行烧录操作了。如图所示,点击此处编译运行。

绑定完成了之后就是去编译运行,运行无错后就可以进行烧录操作了。如图所示,点击此处编译运行。

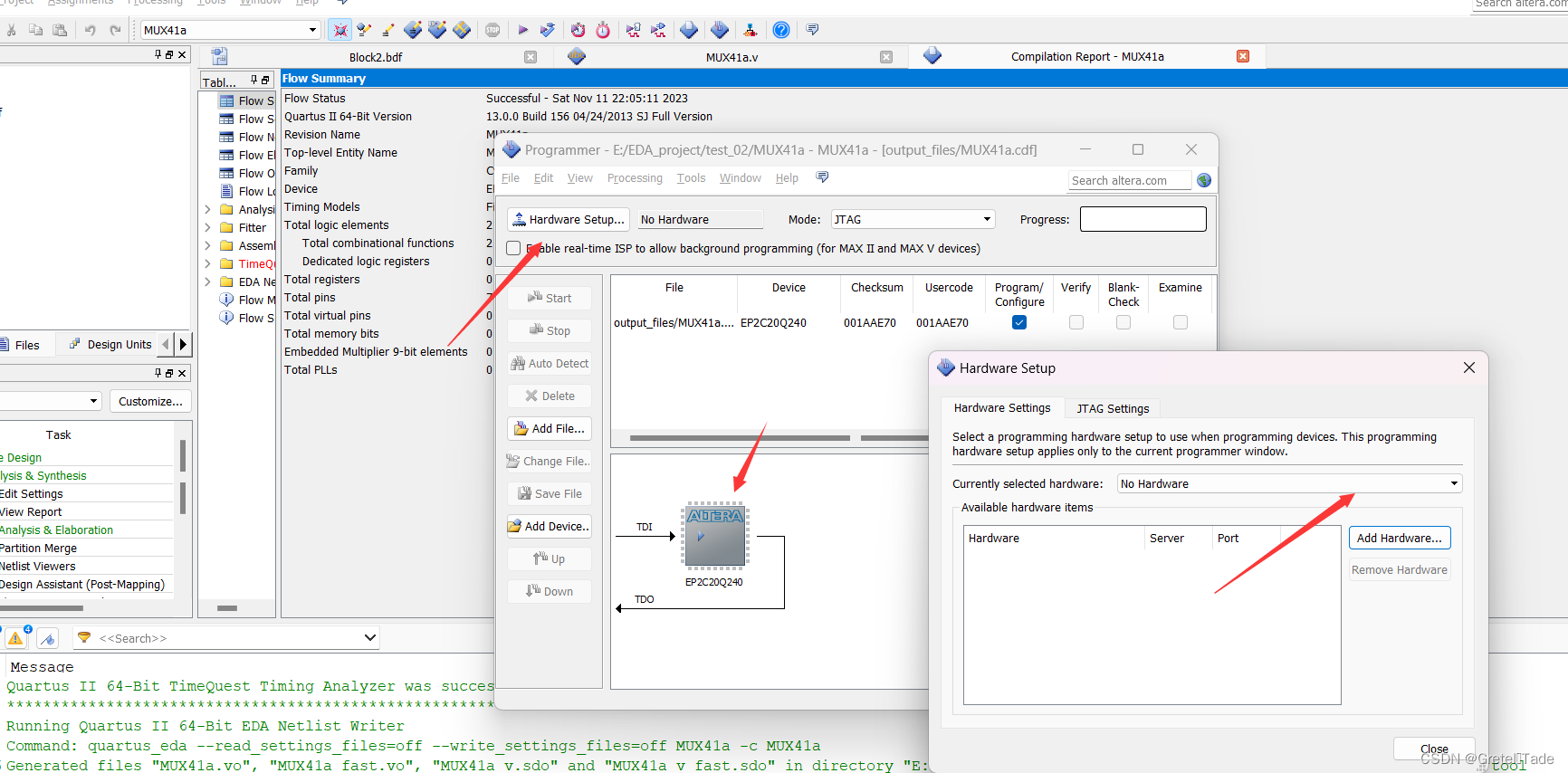

4.烧录文件

点开此处。

这里我们会看到,下面有一个芯片,这个也就是我们写好了的sof文件,然后就是通过你的电脑接口去连接到开发板,如果你看到上面有一个No Hardware的时候,你点击旁边的按钮进行接口设置,设置为USB接口即可。最后点击start就可以进行烧录了。

最后就在开发板去进行检查吧。

最后就在开发板去进行检查吧。

以上就是本期的全部内容了,我们下一次见!

分享一张壁纸: