晶振8MHz,但是处理器输入可以达到72MHz,是因为PLL锁相环提供了72MHz。

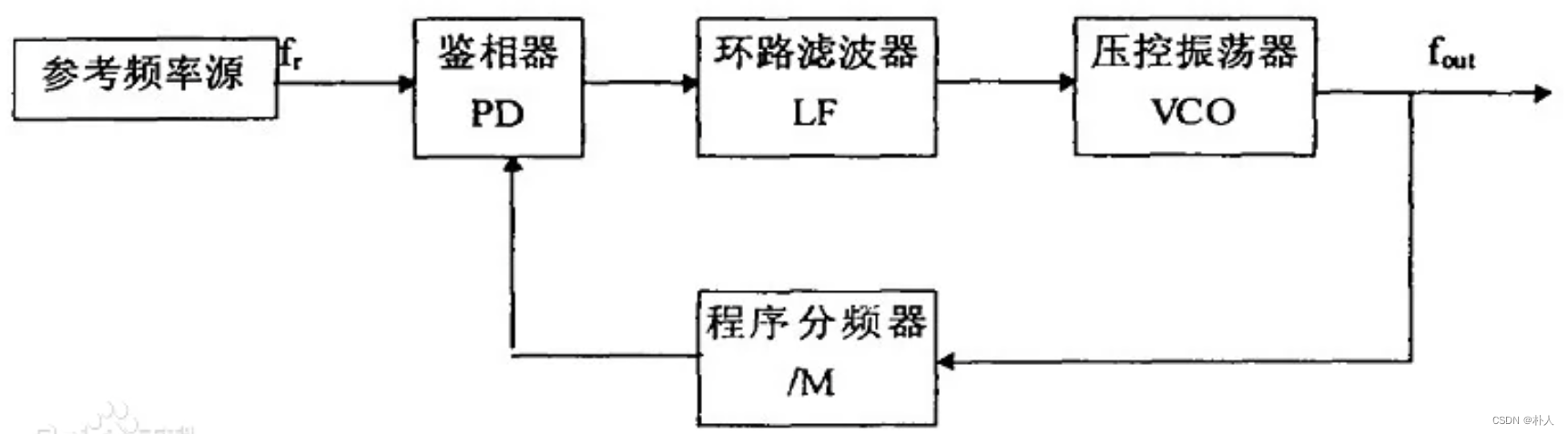

锁相环由PD(鉴相器)、LP(滤波器)、VCO(压控振荡器)组成。

处理器获得的72MHz并非晶振提供,而是锁相环的VCO(压控振荡器)提供。

VCO是一种可以改变电压直接输出非常高频率的模块,但是自身是开环不稳定。

晶振的频率不是用来倍频提供给处理器,而是用作PLL的参考频率。VCO产生超高频率后进行分频,再与晶振频率进行比较,其误差闭环传递给VCO,VCO调节频率(可以用PID调节)到处理器需要的频率。

外部看到的PLL倍频数,比如8MHz倍频9倍到72MHz,实际上是PLL中的VCO分频9倍到8MHz与晶振参考频率比较。所以严格来说,并不是晶振频率倍频了9倍,而是PLL中的VCO生成了一个闭环可控的高频频率。

![[C国演义] 第十三章](https://img-blog.csdnimg.cn/d9080d84e70240d6b48d8a5fbd82b6f3.png)