牛客网Verilog刷题——VL53

- 题目

- 答案

题目

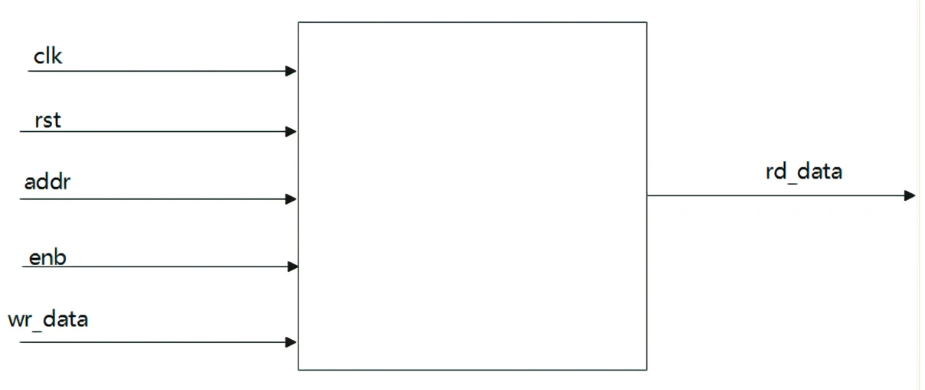

设计一个单端口RAM,它有: 写接口,读接口,地址接口,时钟接口和复位;存储宽度是4位,深度128。注意rst为低电平复位。模块的接口示意图如下。

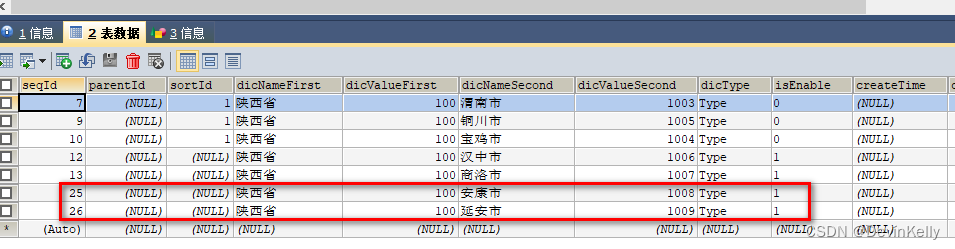

输入输出描述如下。

| 信号 | 类型 | 输入/输出 | 位宽 | 描述 |

|---|---|---|---|---|

| clk | wire | Input | 1 | 系统时钟信号 |

| rst | wire | Input | 1 | 异步复位信号,低电平有效 |

| enb | wire | Input | 1 | 写使能信号 |

| addr | wire | Input | 7 | 读/写地址 |

| w_data | wire | Input | 4 | 写数据 |

| r_data | wire | Output | 4 | 读数据 |

答案

根据读地址的位宽(为7),我们可以知道该单端口RAM的深度为128,所以该RAM是一个宽度为4,深度为128的单端口RAM。需要注意的是:该RAM非写即读,即enb=1,则为写操作;enb=0,则为读操作。

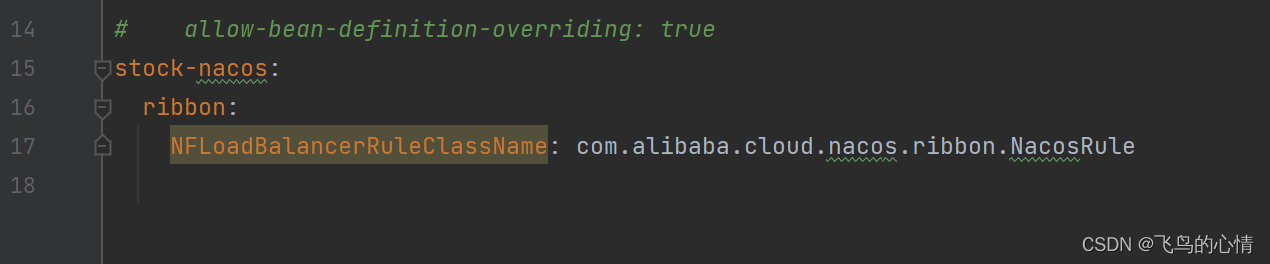

`timescale 1ns/1nsmodule RAM_1port(input clk,input rst,input enb,input [6:0]addr,input [3:0]w_data,output wire [3:0]r_data

);

//*************code***********//

integer i;

reg [3:0] memory [(2<<6)-1:0];always @(posedge clk or negedge rst)if(!rst)for(i=0;i<(2<<6);i=i+1) beginmemory[i] <= 'd0;endelse if(enb)memory[addr] <= w_data;assign r_data = (!enb) ? memory[addr] : 'd0;//*************code***********//

endmodule